# Low-Frequency Noise Assessment of Work Function Engineering Cap Layers in High-k Gate Stacks

C. Claeys, D<sup>1,\*,z</sup> R. Ritzenthaler, T. Schram, H. Arimura, N. Horiguchi, and E. Simoen<sup>2,3,\*\*</sup>

medium, provided the original work is properly cited. [DOI: 10.1149/2.0221902jss]

Engineering the effective work function of scaled-down devices is commonly achieved by the implementation of capping layers in the gate stack. Typical cap layers are  $Al_2O_3$  for pMOSFETs and La-oxide or Mg for nMOSFETs. Besides introducing a dipole layer at the  $SiO_2$ /high- $\kappa$  interface, the in-diffusion of the metal ions may lead to either passivation or generation of traps in the  $SiO_2$ /high- $\kappa$  layer. This paper uses low frequency noise studies to determine the impact of capping layers on the quality of the  $SiO_2$ /HfO2 gate stacks. The influence on the trap profiles of different types of cap layers, different locations of the cap layer (below or on top of the HfO2 dielectric) and the impact of different thermal budgets, typically used for the fabrication of Dynamic Random Access Memory (DRAM) logic devices, are investigated. The differences between several metal oxides are outlined and discussed.

© The Author(s) 2019. Published by ECS. This is an open access article distributed under the terms of the Creative Commons Attribution 4.0 License (CC BY, http://creativecommons.org/licenses/by/4.0/), which permits unrestricted reuse of the work in any

Manuscript submitted December 18, 2018; revised manuscript received February 5, 2019. Published March 5, 2019.

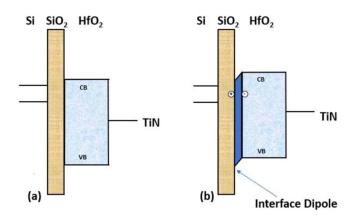

Starting from the 45 nm technology node, the implementation of High-κ/Metal Gate (HK/MG) stacks is common practice for highperformance CMOS devices and circuits. Defects present in the highκ dielectric (e.g. positively charged oxygen vacancies) will strongly influence the value of the threshold voltage (V<sub>T</sub>) of the devices. In order to simplify the process flow, one can choose to implement a single mid-gap work function metal gate like TiN. However, this results in non-optimal V<sub>T</sub> values for either n- or pMOSFETs or both. Engineering of the threshold voltage can be achieved by the implementation of different types of thin capping layers, such as e.g. an Al<sub>2</sub>O<sub>3</sub> or AlN cap for p-channel devices<sup>2-4</sup> and a LaO<sub>x</sub> or MgO<sub>x</sub> cap for n-channel transistors.<sup>5–7</sup> The control of the effective work function is related to the formation of dipoles at the interface between the high-κ dielectric and the interfacial SiO<sub>2</sub> layer underneath.<sup>8–10</sup> A schematic illustration of the location of a dipole layer is shown in Fig. 1. The offset of the bands can influence the density of traps in the dielectric determined from low frequency noise measurements. An atomistic model for the band offset was developed based on ab initio calculations and taking into account the coordination of the interfacial oxygen which depends on technological parameters (e.g. deposition technique, surface passivation) and the used thermal budgets. <sup>10</sup> The diffusion of metal ions (Al, La, Mg...) from the cap layer will, depending on their electronegativity (dipole charge transfer) and ionic radius (dipole separation), alter the dipoles resulting in a shift of the band offset.<sup>11</sup>

It has been reported that in the case of a  $LaO_x$  cap to engineer n-channel devices, a medium to high temperature anneal can reduce the trap density in the  $HfO_2$  layer<sup>12</sup> due to the defect passivation by the  $La.^{13}$  On the other hand, for p-channel devices, the use of an  $Al_2O_3$  cap on a  $HfO_2$  dielectric leads to an increase in the trap density.<sup>14</sup> It is therefore important to investigate more in detail the impact of capping layers on the quality and reliability of the gate stack.

A very powerful diagnostic tool to investigate the quality of the gate stack is low frequency noise analysis. The observed  $1/f^{\gamma}$  or flicker noise  $(\gamma{\sim}1)$  typically found for large area transistors can be either due to carrier trapping in oxide traps (so-called  $\Delta n$  origin)^{15,16} or caused by mobility  $(\mu)$  fluctuations (so-called  $\Delta \mu$  model).  $^{17}$  For smallarea transistors, the current fluctuations in the time domain result in so-called Random Telegraph Noise (RTN).  $^{18-20}$  Both RTN and 1/f noise are commonly used techniques to characterize traps in the gate dielectric. In the first case the energy level, the capture cross section and the trap position with respect to the interface can be revealed for individual oxide defects.  $^{19,20}$  As will be explained below, flicker noise

enables to extract the trap density and depth profile in the oxide under certain assumptions, while determination of the energy distribution and capture cross section is less obvious. The methodology used to extract the oxide trap density profile from the 1/f noise performance is discussed in the next section.

The present work reviews the low-frequency noise of High- $\kappa$ /Metal Gate (HKMG) Metal Oxide Semiconductor Field-Effect Transistors (MOSFETs) with emphasis on the impact of the capping layers used for  $V_T$  tuning. Attention will be given to both  $Al_2O_3$  cap layer engineering in pMOSFETs, and  $LaO_x$  or Mg-based cap layers in n-channel transistors. The influence of different technological parameters will be addressed, with the exception of the choice of the metal gate (TiN, TaN, AlSi....) itself as the impact of this parameter on the 1/f noise performance has recently been reviewed by the authors.  $^{2l-23}$

## Methodology to Determine Trap Parameters from Noise Studies

LF noise measurements have been performed on HfO<sub>2</sub>-based gate stacks, with different types of metal-oxide-based cap layers, using W = 1  $\mu m \times L = 1~\mu m$  (Al<sub>2</sub>O<sub>3</sub> pMOSFETs) or W = 1  $\mu m \times L = 0.170~\mu m$  area devices (p- and nMOSFETs) in linear operation (drain-to-source voltage  $V_{DS} = -0.05~V$ ) with the gate voltage  $V_{GS}$  stepped from weak to strong inversion. Rather large-area transistors have been selected in order to emphasize the 1/f noise behavior and to reduce the noise variability, induced by the presence of RTN. For each device type, about ten devices per wafer have been measured in order to address the noise variability. The drain current noise Power

Figure 1. Energy band diagrams of a Si nMOSFET without (a) and with (b) a dipole at the  $SiO_2/HfO_2$  interface.

<sup>&</sup>lt;sup>1</sup>Department of Electrical Engineering, KU Leuven, B-3001 Leuven, Belgium

<sup>&</sup>lt;sup>2</sup>Imec, B-3001 Leuven, Belgium

<sup>&</sup>lt;sup>3</sup>Department Solid State Sciences, Ghent University, 9000 Ghent, Belgium

$<sup>{\</sup>rm *Electrochemical\ Society\ Fellow}.$

<sup>\*\*</sup>Electrochemical Society Member.

<sup>&</sup>lt;sup>z</sup>E-mail: c.claeys@ieee.org

Spectral Density (PSD) ( $S_I$ ) and its normalized value ( $S_I/I_D^2$ ) have been studied at a fixed frequency f=10 Hz versus the drain current  $I_D$ . The input-referred voltage noise PSD ( $S_{VG}$ ) is derived from  $S_I$  by dividing with  $g_m^2$ , with  $g_m$  the measured transconductance.

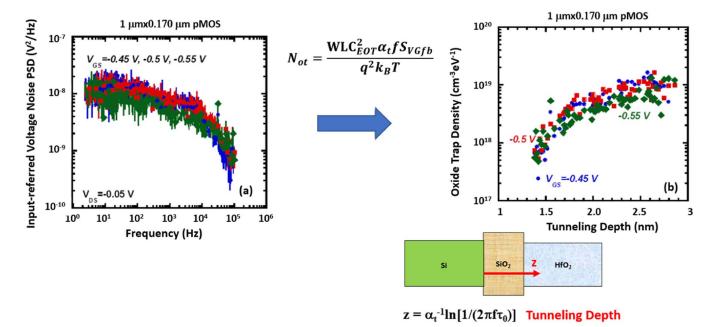

*Trap density.*—In the case that the noise is dominated by carrier number fluctuations (CNF or  $\Delta n$ ), i.e., capturing/emission of carriers by/from traps in the dielectric, the trap density  $N_{ot}$  can be calculated from the 1/f noise PSD using: $^{15,16,24}$

$$N_{ot} = \frac{\text{WLC}_{EOT}^2 \alpha_t f S_{VGfb}}{q^2 k_B T}$$

[1]

with q the elementary charge,  $k_B$  Boltzmann's constant and T the absolute temperature. W and L are the device width and length, respectively,  $C_{EOT}$  is the capacitance density (F/cm²) corresponding with the Equivalent Oxide Thickness (EOT), f is the frequency,  $S_{VGfb}$  is the input-referred voltage noise at flatband voltage and  $\alpha_t$  is the attenuation factor of the electron wave function in the gate oxide. The latter is for an nMOSFET given by  $^{15,16}$

$$\alpha_t = \frac{2}{\hbar} \sqrt{2q m_{ox} \Phi_{it}}$$

[2]

with  $\hbar$  the reduced constant of Planck,  $m_{ox}$  the tunneling effective mass and  $\Phi_{it}$  the barrier height or conduction band offset. Symmetrical relationships hold for holes in a pMOSFET. It can be seen from Eq. 2 that the  $\alpha_t$  value for  $SiO_2$  is different than for a high- $\kappa$  dielectric. For most of the high- $\kappa$  devices, CNF is dominating over mobility fluctuations.  $^{19.25-28}$

**Trap density profile.**—If pure elastic tunneling is assumed then the frequency f can be translated into a trap depth z in the oxide according to

$$z = \alpha_t^{-1} \ln[1/(2\pi f \tau_0)]$$

[3]

with  $\tau_0$  the Shockley-Read-Hall recombination lifetime at the Si/SiO<sub>2</sub> interface, given by

$$\tau_0 = \frac{1}{n\sigma_n \nu_{thn}}$$

[4]

with *n* the (volume) free carrier density in the inversion layer,  $v_{\text{thn}}$  the thermal velocity and  $\sigma_n$  the capture cross section for electrons.

Usually, a value of  $10^{-10}$  s is assumed. A 1/f noise spectrum can then be converted in an oxide trap density profile as follows: Eq. 1 transforms the noise PSD into an  $N_{ot}$  (cm $^{-3}$  eV $^{-1}$ ), while Eq. 3 converts the frequency axis into a trap depth with respect to the Si/SiO $_2$  interface. This approach is illustrated in Fig. 2. The lower the frequency the deeper the trap into the oxide. It should be remarked that for the same measurement frequency the trap depth is larger in n-channel devices than for p-channel devices due to the different tunneling barrier for electrons and holes, respectively.

In case that the capture time  $\tau_{\text{c}}$  is thermally activated Eq. 4 becomes

$$\tau_c = \tau_0 \exp\left(\frac{E_B}{k_B T}\right) \exp\left(\alpha_t z\right)$$

[5]

with  $E_B$  the energy barrier for capture by an oxide trap. Unless  $E_B/k_BT <<1$  one is dealing with inelastic tunneling and the energy level of the trap  $E_T$  has to be taken into account for calculating the depth, resulting in the following expression<sup>29</sup>

$$z = \frac{1}{\alpha_t} \ln \left[ \frac{1}{2\pi f_0 \tau_0} \frac{1 + \exp\left(\frac{E_T - E_F}{k_B T}\right)}{\exp\left(\frac{E_B}{k_B T}\right)} \right]$$

[6]

with  $f_0$  the corner frequency of the spectrum. As this analysis is only feasible for RTN, the trap density profiles will be derived from the 1/f noise spectra under the elastic tunneling assumption.

## Impact Capping Layer on Low Frequency Noise Performance

This section gives a systematic study of the impact of the implementation of capping layers for  $V_T$  engineering on the low frequency noise and, therefore, on the quality of the gate stack. Various process conditions will be investigated, including the position of the cap layer in the stack gate, i.e., above or below the high- $\kappa$  dielectric, and the thermal budget of the post gate stack deposition, implemented in a Dynamic Random Access Memory (DRAM) process flow. During the thermal processing the metal atoms from the capping layer will diffuse and therefore modify the dipoles at the SiO\_2/HfO\_2 interface by the bond dipole effect.

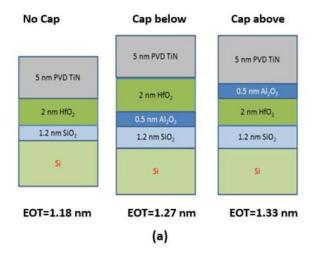

The work is focussing on  $HfO_2$  gate dielectrics (1.2 nm  $SiO_2$  interfacial oxide and 2 nm  $HfO_2$  with a 5 nm TiN metal gate) using  $Al_2O_3$

Figure 2. Principle of border trap profiling under the assumption of elastic tunneling to traps in the oxide. The input-referred voltage noise PSD (a) is the basis to calculate from its flatband value the oxide trap density, while the frequency is converted into a depth scale enabling to determine the trap profile (b).

**Figure 3.** Gate stack configuration for the pMOSFETs without or with a 0.5 nm Al $_2$ O $_3$  cap layer (a) and (b) corresponding border trap density profile for 1  $\mu$ mx1  $\mu$ m pMOSFETs derived from a 1/f $^\gamma$  spectrum around threshold voltage  $V_T$ .

and La-oxide or Mg as a capping layer for p- and n-channel devices, respectively. This gate stack is typically used for DRAM peripheral logic devices.

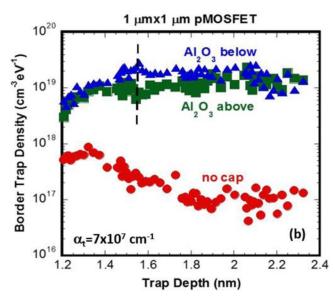

$Al_2O_3$  for pMOS work function tuning.—First the location of the 0.5 nm  $Al_2O_3$  cap, i.e., below or above the HfO<sub>2</sub> layer as shown in Fig. 3a, was studied. The corresponding border trap profiles are given in Fig. 3b, taking into account an attenuation factor of  $7 \times 10^7$  cm<sup>-1</sup> for the HfO<sub>2</sub> dielectric. In the case of a capping layer underneath the high-κ dielectric, a different attenuation factor has to be used for the cap layer and the dielectric. The depth scale used in Fig. 3b is selected in order to illustrate the trap profile in the gate dielectric. It can clearly be seen that i) the use of a capping layer increases the trap density and ii) an  $Al_2O_3$  layer on top of the HfO<sub>2</sub> dielectric is beneficial compared to the layer below.

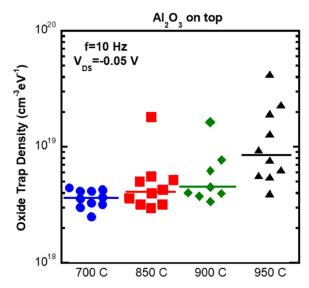

The impact of a high temperature anneal, as typically used during DRAM processing, is shown in Fig. 4 for a cap layer on top. This step results in a diffusion of Al into the high- $\kappa$  layer. The figure indicates that for a capping layer on top of the high- $\kappa$  dielectric there is up to about 900°C only a slight impact of the anneal temperature on the average border trap density. There is, however, a pronounced

**Figure 4.** Oxide trap density for DRAM peripheral pMOSFETs with  $Al_2O_3$  cap above the high- $\kappa$  layer as a function of the diffusion annealing temperature. The noise measurements have been performed in linear operation ( $V_{DS}=-0.05\ V)$  on 1  $\mu mx0.170\ \mu m$  pMOSFETs. The oxide trap density has been derived from the  $S_{VG}$  at  $f=10\ Hz$  in the flatband part of the  $S_{VG}$  versus  $V_{GS}$  characteristic. The solid lines are referring to the median values.

increase in both median trap density and spread in the data for higher temperatures. A possible interpretation could be that the anneal effect of the temperature treatment is reduced by the in-diffusion of Al. Another factor which could play a role is the crystallization of the  $HfO_2$  at higher anneal temperatures that could introduce grain boundaries and, hence, more noisy traps.

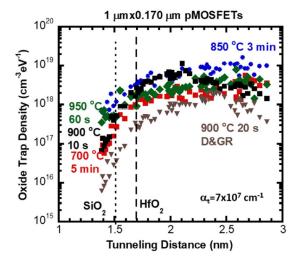

The used frequency of 10 Hz in Fig. 4 corresponds with a trap depth well located in the HfO<sub>2</sub> layer. By extending the frequency range detailed trap profiles are obtained as shown in Fig. 5 for different anneal conditions. It is clearly seen that the trap density reduces near the SiO<sub>2</sub>/HfO<sub>2</sub> interface. A lower trap density is found for a lower anneal temperature. Assuming that the lower trap density corresponds to the SiO<sub>2</sub> IL, one can estimate the position of the interface with HfO<sub>2</sub>, to be somewhere between 1.5 and 1.7 nm, as indicated by the

**Figure 5.** Oxide trap density profile derived from a LF noise spectrum around threshold voltage for DRAM peri pMOSFETs with  $Al_2O_3$  cap layer on top and corresponding with different diffusion anneal temperatures. The dashed and dotted lines indicate the boundaries for the position of the  $SiO_2/HfO_2$  interface.

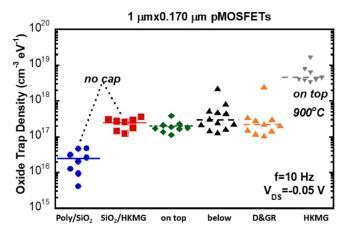

**Figure 6.** Oxide trap density at f=10 Hz, derived from the input-referred noise measured in linear operation ( $V_{DS}=-0.05$  V) in the flatband voltage part on 1  $\mu$ mx0.170  $\mu$ m pMOSFETs with different gate stack: polysilicon/5 nm SiO<sub>2</sub> references (blue symbols); 5 nm SiO<sub>2</sub> + 2 nm HfO<sub>2</sub> + 5 nm TiN (red symbols); 5 nm SiO<sub>2</sub> + 2 nm HfO<sub>2</sub> + 0.5 nm Al<sub>2</sub>O<sub>3</sub> + 5 nm TiN (green symbols); 5 nm SiO<sub>2</sub> + 0.5 nm Al<sub>2</sub>O<sub>3</sub> + 2 nm HfO<sub>2</sub> + 5 nm TiN (black symbols); D&GR scheme (orange symbols) and 1.2 nm SiO<sub>2</sub> + 2 nm HfO<sub>2</sub> + 0.5 nm Al<sub>2</sub>O<sub>3</sub> + 5 nm TiN (grey inverted triangle symbols). The solid and dashed lines are median values.

dotted and dashed lines in Fig. 5. It is even a bit lower in Fig. 3b. This allows to estimate an error in the trap density position in the range of 0.3 to 0.5 nm by using the elastic tunneling model of Eq. 3. In other words, using the 1.2 nm SiO<sub>2</sub> thickness as a kind of marker, one can estimate the possible inaccuracy of the trap density derived from 1/f noise, using the procedure derived above. This will become even more clear for the nMOSFET data reported below.

To obtain a good insight in the importance of the position of the capping layer complementary electrical investigations were performed and resulted in the following conclusions:  $^{25}$  i) the defect density profiles derived from the low frequency noise and charge pumping current are in agreement with what can be expected from traps related to Al diffusion, and ii) the highest peak density of traps depends on the location where the  $Al_2O_3$  cap is inserted, i.e., for a layer below the high- $\kappa$  there is a higher trap density in the  $SiO_2$  layer, while for a layer on top there is a higher trap density in the  $HfO_2$ . Compared to the reference condition without a cap layer, using an  $Al_2O_3$  cap layer results in a slightly higher trap density, slightly lower performances and shorter NBTI lifetime. However, the  $Al_2O_3$  position has only a marginal impact on the NBTI reliability but increased leakage current and reduced LF noise for  $Al_2O_3$  below  $HfO_2$ . Overall, preference is given to a top layer

There is a tendency for thick oxide DRAM peripheral (peri) Input/Output (I/O) pMOSFETs to make these devices compatible with the gate stack of the DRAM peri logic devices, implying that one wants to replace the standard thick-SiO<sub>2</sub>/polysilicon combination by a SiO<sub>2</sub>/HfO<sub>2</sub>/ metal-gate stack.<sup>20</sup> Therefore, a comparison is made between the two process options either 5 nm  $SiO_2$ /poly Si or 5 nm  $SiO_2$  +  $2 \text{ nm HfO}_2 + \text{TiN metal gate}$ . In the latter case,  $V_T$  tuning is performed by a thin Al<sub>2</sub>O<sub>3</sub> cap either on top or below the high-κ layer. Figure 6 presents the spread in trap density and its median value while Fig. 7 shows the trap profiles, derived from the 1/f-like noise spectra around V<sub>T</sub>. The data confirms previous observations that a high-κ stack has a lower quality than the thick SiO<sub>2</sub>, while the additional degradation by inserting an Al<sub>2</sub>O<sub>3</sub> cap is limited. There are in Fig. 6 two conditions with a cap layer on top, i.e., one with 5 nm SiO<sub>2</sub> (green symbols) and one with 1.2 nm SiO<sub>2</sub> (grey inverted triangle symbols). As the frequency is 10 Hz (about 2 nm depth) one measures the trap density in the SiO<sub>2</sub> layers in the first case, while this is in the HfO<sub>2</sub> layer for the second condition. This explains the higher trap density for the latter pMOSFETs. A Diffusion and Gate Replacement (D&GR) integration scheme, based on a diffusion anneal step of the SiO<sub>2</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>

**Figure 7.** Oxide trap density profile derived from the low-frequency noise spectra of a pMOSFET for each split with 5 nm SiO<sub>2</sub> at  $V_{GS} \sim V_T$  and  $V_{DS} = -0.05$

stack before removing the cap layer and subsequently depositing the metal gate,  $^{30}$  does not introduce a significant degradation of the  $\mathrm{SiO}_2$  in Figs 6 and 7. The advantage of the D&GR process is that the drive-in step can be done simultaneously for the p- and n-channel cap layers.

The different trap profile at longer depths for the  $HfO_2$  case (Fig. 7) may be caused by the possible in-diffusion of Hf from the high- $\kappa$  dielectric into the underlying  $SiO_2$  layer resulting in the decaying profile toward the interface. Another reason could be the presence of generation-recombination noise causing humps in the 1/f spectra and add to the observed spread from device-to device. The latter may lead to a range of trap densities at each depth. The main goal of the study presented here is to outline the general differences between the  $SiO_2/poly$  devices and the other splits so that no further in-depth analyses have been performed. As a general conclusion it can be stated that when the  $poly/SiO_2$  stack is replaced by a high- $\kappa$  dielectric then preference is given to a top capping layer with a moderate temperature anneal. Compared to  $Al_2O_3$  below the  $HfO_2$  layer there is a reduction in the leakage current and increase in low frequency noise, while the NBTI reliability is not compromised.<sup>25</sup>

La-oxide or Mg caps for nMOS work function tuning.—The improved threshold voltage and device performance by using an ALD La<sub>2</sub>O<sub>3</sub> capping layer to tune HfSiON/metal gate nMOSFETs has been reported by several authors. <sup>6,31-34</sup> It was also observed that the presence of the cap reduces the 1/f PSD. <sup>13</sup> This has been interpreted as a reduction by La of the effective trap density in the dielectric either by passivation of the defects or by shifting the energy levels outside the accessible window for 1/f noise through the formation of a dipole. <sup>13,34</sup>

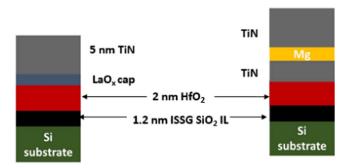

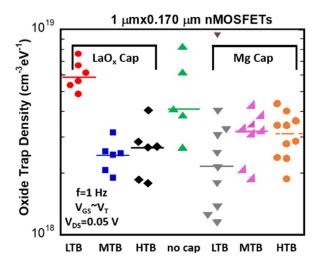

For the first set of experiments reported here, the work function tuning of n-channel transistors is accomplished by either an Atomic Layer Deposition of a  $\text{LaO}_x$  cap on top of the  $\text{HfO}_2$  or the use of a Mg cap, inserted in the TiN metal gate. Both processes are schematically illustrated in Fig. 8. Different thermal anneals are used to control the  $V_T$  shift, i.e., 275 mV (Low Thermal Budget - LTB), 175 mV (Medium - MTB) and 125 mV (High - HTB), respectively.

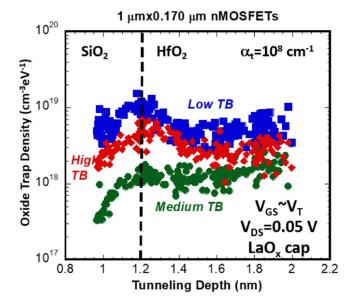

Figure 9 shows the border trap density profile for the three different anneals of the  $LaO_x$  cap layer, clearly indicating the impact of the thermal budget. A medium temperature anneal leads to the lowest trap density, while the density increases for higher thermal budgets.

For La there is a correlation between the La diffusion and the trap density. Based on Time-of-Flight Secondary Ion Mass Spectrometry (ToF-SIMS) measurements the diffusivity of La in HfSiON has been

Figure 8. Schematic gate stack structure of the  $LaO_x$  cap (left) and Mg cap (right) for the  $V_T$  control of nMOSFETs.

reported as

$$D_{La} = 12.5 \times 10^{-10} \exp\left(\frac{1.04 \text{ eV}}{k_B T}\right) \text{ cm}^2 \text{s}^{-1}$$

[7]

indicating that La is a rather fast diffuser in these high- $\kappa$  oxides. These authors observed that besides a thermally activated diffusion mechanism leading to the migration of La from the La<sub>2</sub>O<sub>3</sub> capping layer to the HfSiON/SiO<sub>2</sub> interface, there is also a kinetic reaction mechanism acting due to the LaSiO dipoles formation at the interface. Due to the formation of the dipoles there is no La diffusion in the SiO<sub>2</sub> layer.  $^{36}$

The strong temperature dependence of the La behavior has also been observed for the Al behavior when  $Al_2O_3$  is used as cap for p-channel devices.<sup>37</sup> The metal diffuses to the interface altering the dipole behavior required for the  $V_T$  tuning and it will also introduce additional traps in the  $HfO_2$  layer.

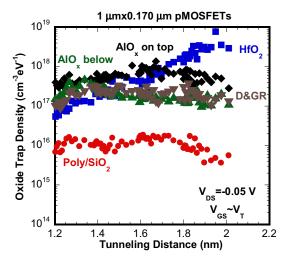

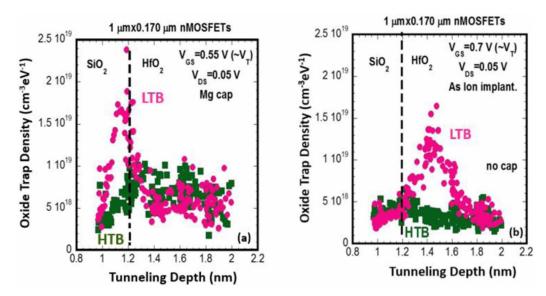

Similar experiments have been performed for devices with a Mg cap. The border trap profiles are shown in Fig. 10a. It can be noticed that with a Mg cap there is a density peak near the  $SiO_2/HfO_2$  interface (Fig. 10a) after the low budget anneal, which is eliminated by a higher thermal anneal (900°C). The trap density in the  $HfO_2$  layer at larger depths is, for the transistors displayed in Fig. 10a, not influenced by the thermal budget of the anneal step.

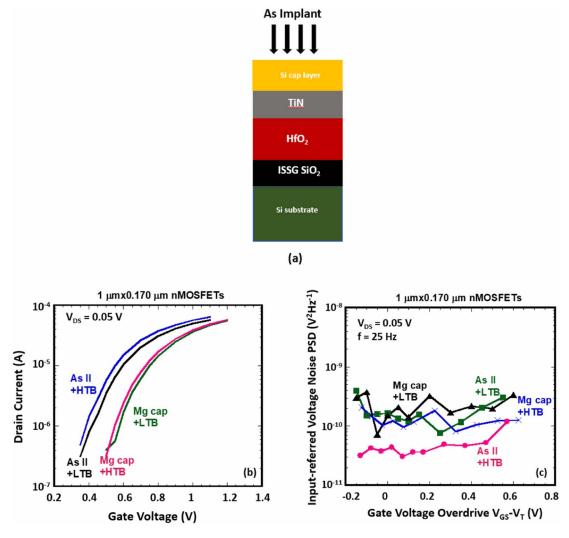

It is interesting to compare the trap profile behavior for a Mg cap with the process condition when using an As implantation to tune the effective work function, by passivation of the oxygen vacancies (defects). 38,39 Implanting As in a nitrided-metal gate layer (e.g. TiN

**Figure 9.** Border trap density calculated from the normalized input-referred voltage noise PSD for DRAM peri nMOSFETs with a  $LaO_x$  cap on top of the  $HfO_2$  and corresponding with different diffusion thermal budgets.

or TaN) through an amorphous Si buffer layer, as shown in Fig. 11a, releases nitrogen from the metal and passivates the deep traps in the high- $\kappa$  layer. 40 Ab-initio calculations confirm that nitrogen-passivated defects are shifting to energetically shallower states. 41

The impact of the used tuning technique on the drain current is shown in Figure 11b for both the Mg cap and As implant. It can be noticed that the different curves have the same shape and only show a small impact of the used thermal budget. The shift of the curves to higher gate voltage values for the Mg cap is due to the shift of the threshold voltage (As II LTB = 0.65 V, As II HTB = 0.63 V) compared to the Mg cap (Mg LTB = 0.5 V and Mg HTB = 0.475 V). The influence of the threshold voltage tuning technique on the inputreferred voltage noise PSD is given in Fig. 11c. The lowest noise level is observed for the As I/I HTB case, while reducing the thermal budget leads in both cases to an increase of the input-referred voltage noise, for the displayed devices. To calculate the trap density from the S<sub>VG</sub> values at flatband, the values have to be normalized by the EOT of the stacks. Therefore the trend related to the noise may be different than the trend in trap density. It should be noted that a different trend appears for the Mg cap nMOSFETs when comparing all available data (see Fig. 12). An observed trend for selected devices may deviate from a general trend based on the study of a large number of devices due to the statistics involved. This is especially the case for sensitive parameters such as low frequency noise.

Figure 10b shows for the As implant approach the trap density profile for two different thermal anneals. Compared to Fig. 10a it can be seen that that the density peak, which is not located at the interface in this case but in the HfO<sub>2</sub>, anneals out for higher temperatures. Figure 10 allows to conclude that the trap density in the HfO<sub>2</sub>, away from the interface with SiO<sub>2</sub> is not sensitive to the thermal budget in both cases, for the selected devices. At the same time, the lower value in the As ion implantation case (5  $\times$  10<sup>18</sup> cm<sup>-3</sup> eV<sup>-1</sup> compared with ~2.5  $\times$  10<sup>18</sup> cm<sup>-3</sup> eV<sup>-1</sup>) confirms the anticipated N passivation effect. The main influence of the temperature during the post-deposition DRAM anneal is the removal of the defect peak, occurring around the SiO<sub>2</sub>/HfO<sub>2</sub> interface for both the Mg and As ion implantation nMOSFETs in Fig. 10. Again, a possible range of the SiO<sub>2</sub>/HfO<sub>2</sub> interface between 1.2 to 1.5 nm can be derived from the defect peak position, assuming that it corresponds approximately with this position.

Finally, Fig. 12 gives a comparison of the average trap densities observed for both  $LaO_x$  and Mg caps. The used measurement frequency of 1 Hz corresponds with a depth of 2 nm, i.e., located about 0.8 nm in the HfO<sub>2</sub> layer. Within the group of  $LaO_x$  cap nMOSFETs the lowest average (and median) trap density is found for the M- or HTB, which also removes the defect peak in Fig. 10. The opposite trend is found for the Mg nMOSFETs in Fig. 12: the lowest median  $N_{ot}$  for the LTB, however, corresponding with a larger dispersion; slightly higher values are found for the M- and HTB, which are on the average about 40% smaller than for the reference devices. Overall, compared to La, there may be for Mg a different behavior for the interaction between the metal and the defects (most likely oxygen vacancies) in the high- $\kappa$  dielectric.

#### Summary

An overview has been given on the impact of the use of a metal oxide cap layer to tune the threshold voltage of transistors with  $SiO_2/HfO_2$  gate stacks. Both  $Al_2O_3$  (pMOS) and La-oxide or Mg (nMOS) were studied, pointing out their impact on the quality of the gate stacks by influencing the profile of the traps in the dielectric. Beside the type of capping layer, its position in the gate stack and also the thermal budget used during the device fabrication have a strong impact on the final result. The low frequency noise studies pointed out that besides affecting the dipole layer at the interface, key for tuning the effective work function, also the diffusion behavior of the metal during thermal treatments is impacting the passivation of traps and/or generation of additional oxide traps in the  $HfO_2$  layer. A different behavior is observed for Mg compared to La, making the first one more temperature insensitive thereby less impacting the trap profile in the bulk.

Figure 10. (a) Oxide trap density profile for DRAM peri nMOSFETs with a Mg diffusion shifter and corresponding with a low thermal budget (LTB) or a high thermal budget (HTB). (b) Oxide trap density profile for DRAM peri nMOSFETs with an As ion implantation in the nitrided-metal gate and corresponding with a low thermal budget (LTB) or a high thermal budget (HTB).

Figure 11. (a) Schematic gate stack structure for the As implantation approach (a) and impact of the approach on the drain current in comparison with the Mg cap technique, for different thermal treatments (b). The influence of the As implant and Mg cap conditions on the input-referred voltage noise PSD is also shown for a low and a high thermal budget (c).

**Figure 12.** Oxide trap density corresponding with f=1 Hz ( $\sim 2$  nm depth) for 1  $\mu$ mx0.170  $\mu$ m nMOSFETs with LaO<sub>x</sub> or Mg cap. Reference HKMG nMOSFETs without cap layer are also included. The solid lines are median values.

For DRAM applications, the best option remains the poly/SiO $_2$  stack. However, when for a better compatibility with CMOS processing the poly/SiO $_2$  stack is replaced by a high- $\kappa$  dielectric then preference is given to a top capping layer with a moderate temperature anneal. Compared to  $Al_2O_3$  below the HfO $_2$  layer there is a reduction in the leakage current and increase in low frequency noise, while the NBTI reliability is not compromised. Not only the trap behavior studied here, but all the different performance parameters have to be taken into account for selecting the most appropriate threshold voltage tuning approach for a particular application.

# Acknowledgments

This work has been performed in imec's Core Partner Program on DRAM peri. In addition, we thank M. Jurczak, A. Thean, M. Aoulaiche, P. Fazan, A. Federico, M.-J. Cho, T. Kauerauf, G. Groeseneken, F. Crupi, A. Spessot, C. Caillat, Y. Son and K. B. Noh for the use of co-authored results.

# ORCID

C. Claeys https://orcid.org/0000-0002-6634-4709

## References

- K. Mistry, C. Allen, C. Auth, B. Beattie, D. Bergstrom, M. Bost, M. Brazier, M. Buehler, A. Cappellani, R. Chau, C.-H. Choi, G. Ding, K. Fischer, T. Ghani, R. Grover, W. Han, D. Hanken, M. Hattendorf, J. He, J. Hicks, R. Huessner, D. Ingerly, P. Jain, R. James, L. Jong, S. Joshi, C. Kenyon, K. Kuhn, K. Lee, H. Liu, J. Maiz, B. McIntyre, P. Moon, J. Neirynck, S. Pae, C. Parker, D. Parsons, C. Prasad, L. Pipes, M. Prince, P. Ranade, T. Reynolds, J. Sandford, L. Shifren, J. Sebastian, J. Seiple, D. Simon, S. Sivakumar, P. Smith, C. Thomas, T. Troeger, P. Vandervoorn, S. Williams, and K. Zawadzki, in *IEDM Tech. Dig.*, The IEEE (New York), 274 (2007)

- S. C. Song, Z. B. Zhang, M. M. Hussain, C. Huffman, J. Barnett, S. H. Bae, H. J. Li, P. Majhi, C. S. Park, B. S. Ju, H. K. Park, C. Y. Kang, R. Choi, P. Zeitzoff, H. H. Tseng, B. H. Lee, and R. Jammy, in VLSI Symp. Tech. Dig., 13 (2006).

- V. S. Chang, L.-Å. Ragnarsson, H. Y. Yu, M. Aoulaiche, T. Connard, K. M. Kim, J. W. Maes, T. Schram, S. De Gendt, and S. Biesemans, *IEEE Trans. Electron Dev.*, 54, 2738 (2007).

- 4. H. N. Alshareef, H. F. Luan, K. Choi, H. R. Harris, H. C. Wen, M. A. Quevedo-Lopez, P. Maihi and R. H. Lee, Appl. Phys. Lett. 88, 112114 (2006)

- P. Majhi, and B. H. Lee, *Appl. Phys. Lett.*, **88**, 112114 (2006).

5. H. Alshareef, M. Quevedo-Lopez, H. C. Wen, R. Harris, P. Kirsch, P. Majhi, B. H. Lee, R. Jammy, D. J. Lichtenwalner, J. S. Jur, and A. I. Kingon, *Appl. Phys. Lett.*, **89**, 232103 (2006).

- V. Narayanan, V. K. Paruchuri, N. A. Bojarczuk, B. P. Linder, B. Doris, Y. H. Kim, S. Zafar, J. Stathis, S. Brown, J. Arnold, M. Copel, M. Steen, E. Cartier, A. Callegari,

- P. Jamison, J.-P. Locquet, D. L. Lacey, Y. Wang, P. E. Batson, P. Ronsheim, R. Jammy, M. P. Chudzik, M. Ieong, S. Guha, G. Shahidi, and T. C. Chen, in *VLSI Symp. Tech. Dia* 224 (2006)

- L.-Å. Ragnarsson, V. S. Chang, Y. Y. Hong, H.-J. Cho, T. Conard, K. M. Yin, A. Delabie, J. Swerts, T. Schram, S. De Gendt, and S. Biesemans, *IEEE Electron Device Lett.*, 28, 486 (2007).

- 8. J. Robertson, J. Vac. Sci. Technol. B, 27, 277 (2009).

- 9. A. Toriumi and T. Nabatame, ECS Trans., 25(6), 3 (2009).

- 10. O. Sharia, A. Demkov, G. Bersuker, and B. H. Lee, *Phys. Rev. B*, **75**, 035306 (2008).

- P. D. Kirsch, P. Sivasubramani, J. Huang, C. D. Young, M. A. Quevedo-Lopez, H. C. Wen, H. Alshareef, K. Choi, C. S. Park, K. Freeman, M. M. Hussain, G. Bersuker, H. R. Harris, P. Majhi, R. Choi, P. Lysaght, B. H. Lee, H.-H. Tseng, R. Jammy, T. S. Böscke, D. J. Lichtenwalner, J. S. Jur, and A. I. Kingon, Appl. Phys. Lett., 92, 092901 (2008).

- E. Simoen, R. Ritzenthaler, T. Schram, M. Aoulaiche, A. Spessot, P. Fazan, H.-J. Na, S.-G. Lee, Y. Son, K. B. Noh, H. Arimura, N. Horiguchi, A. Thean, and C. Claeys, *Proc. ICSICT*, IEEE Xplore, 1631 (2014).

- E. Simoen, A. Akheyar, E. Rohr, A. Mercha, and C. Claeys, *ECS Trans.*, 25(7), 237 (2009).

- E. Simoen, R. Ritzenthaler, M.-J. Cho, T. Schram, N. Horiguchi, M. Aoulaiche, A. Spessot, P. Fazan, and C. Claeys, ECS J. Solid-St. Science and Technol., 5, N27 (2016).

- G. Ghibaudo, O. Roux, Ch. Nguyen-Duc, F. Balestra, and J. Brini, *Phys. Status Solidi A*, 124, 571 (1991).

- T. Boutchacha, G. Ghibaudo, G. Guégan, and M. Haond, J. Non-Cryst. Solids, 216, 192 (1997).

- 17. F. N. Hooge, *IEEE Trans. Electron Devices*, 41, 1926 (1994).

- 18. M. J. Kirton and M. J. Uren, *Adv. in Phys.*, **38**, 367 (1989).

- E. Simoen, H.-C. Lin, A. Alian, G. Brammertz, C. Merckling, J. Mitard, and C. Claeys, *IEEE Trans. Device and Mater. Reliability*, 13, 444 (2013).

- E. Simoen and C. Claeys, "Random Telegraph Signals in Semiconductor Devices", The Institute of Physics (Bristol) (2016).

- W. Fang, A. Veloso, E. Simoen Moon-Ju Cho, N. Collaert, A. Thean, J. Luo, C. Zhao, T. Ye, and C. Claeys, *IEEE Electron Dev. Lett.*, 37, 363 (2016).

- C. Claeys, L. He, B. J. O'Sullivan, A. Veloso, N. Horiguchi, N. Collaert, and E. Simoen, ECS J. Solid-St. Science and Technol., 7, Q26 (2018).

- E. Simoen, B. O'Sullivan, R. Ritzenthaler, E. Dentoni Litta, Schram T., Horiguchi N., and Claeys C., *IEEE Trans. Electron Devices*, 65, 3676 (2018).

- 24. E. Simoen and C. Claeys, Solid-State Electron., 43, 865 (1999).

- M. Aoulaiche, E. Simoen, R. Ritzenthaler, T. Schram, H. Arimura, M. Cho, T. Kauerauf, G. Groeseneken, N. Horiguchi, A. Thean, A. Federico, F. Crupi, A. Spessot, C. Caillat, P. Fazan, H.-J. Na, Y. Son, and K. B. Noh, *Proc. of ESSDERC* 2013, IEEE Explore, 190 (2013).

- C. Claeys, E. Simoen, A. Mercha, L. Pantisano, and E. Young, J. Electrochem. Soc., 152, F115 (2005).

- B. Min, S. P. Devireddy, Z. Çelik-Butler, A. Shanware, L. Colombo, K. Green, J. J. Chambers, M. R. Visokay, and A. L. Pacheco Rotondaro, *IEEE Trans. Electron Devices*, 53, 1459 (2006).

- T. Morshed, S. P. Devireddy, Z. Çelik-Butler, A. Shanware, K. Green, J. J. Chambers, M. R. Visokay, and L. Colombo, *Solid-State Electron.*, 52, 711 (2008).

- 29. E. Simoen, J. W. Lee, and C. Claeys, IEEE Trans. Electron Devices, 61, 634 (2014).

- R. Ritzenthaler, T. Schram, A. Spessot, C. Caillat, M. Cho, E. Simoen, M. Aoulaiche, J. Albert, S. Chew, K. Noh, Y. Son, P. Fazan, N. Horiguchi, and A. Thean, *IEEE Trans. Electron Devices*, 63, 265 (2016).

- H. Alshareef, H. R. Harris, H. C. West, C. S. Park, C. Huffman, K. Choi, H. F. Luan, P. Majhi, B. H. Lee, R. Jammy, D. J. Lichtenwalner, J. S. Jur, and A. I. Kingon, in VLSI Symp. Tech. Dig., 7 (2006).

- P. D. Kirsch, M. A. Quevedo-Lopez, S. A. Krishnan, C. Krug, H. Alshareef, C. S. Park, R. Harris, N. Moumen, A. Neugroschel, G. Bersuker, H. Lee, J. G. Wang, G. Pantl, B. E. Gnade, M. J. Kim, R. M. Wallace, J. S. Jur, D. J. Lichtenwalner, A. I. Kingon, and R. Jammy, in *IEDM Techn. Dig.*, The IEEE (New Y0rk), 629 (2006)

- P. T. S. Boscke Sivasubramani, J. Huang, C. D. Young, P. D. Kirsch, S. A. Krishnan, M. A. Quevedo-Lopez, S. Govindarajan, B. S. Ju, H. R. Harris et al., in *VLSI Symp. Tech. Dig.*, 68 (2007).

- 34. S. Kamiyama, E. Kurosawa, and Y. Nara, *J. Electrochem. Soc.*, **155**, H373 (2008).

- Z. Essa, C. Gaumer, A. Pakfar, M. Gros-Jean, M. Juhel, F. Panciera, P. Boulenc, C. Tavernier, and F. Cristiano, Appl. Phys. Lett., 101, 182901 (2012).

- R. Leitsmann, F. Lazarevic, M. Drescher, and E. Erben, J. Appl. Phys., 121, 234501 (2017).

- E. Simoen, A. Federico, M. Aoulaiche, R. Ritzenthaler, T. Schram, H. Arimura, M.-J. Cho, T. Kauerauf, G. Groeseneken, N. Horiguchi, A. Thean, F. Crupi, A. Spessot, C. Caillat, P. Fazan, Y. Son, and K. B. Noh, Semicond. Sci. and Technol., 29, 115015 (2014).

- R. Ritzenthaler, T. Schram, A. Spessot, A. Caillat H.-J Na, S.-G. Lee, SK. Noh Y.Son, M. Aoulaiche, H. Arimura, N. Horiguchi, P. Fazan, and A. Thean, *Proc. IEEE Work-shop on Microelectron. and Devices*, IEEE Explore (2014).

- E. Simoen, R. Ritzenthaler, T. Schram, M. Aoulaiche, A. Spessot, P. Fazan, H.-J. Na, S.-G. Lee, Y. Son, K. B. Noh, N. Horiguchi, A. Thean, and C. Claeys, *Proc. of CSTIC* 2015, IEEE Explore (2015).

- C. Ortolland, S. Sahhaf, V. Srividya, R. Degraeve, K. Saino, C. S. Kim, M. Gilbert, T. Kauerauf, M. J. Cho, M. Dehan, T. Schram, M. Togo, N. Horiguchi, G. Groeseneken, S. Biesemans, P. P. Absil, W. Vandervorst, D. Gealy, and T. Hoffmann, in VLSI Symp. Tech. Dig., 185 (2010)

- 41. K. Xiong, J. Robertson, and S. J. Clark, J. Appl. Phys., 99, 044105 (2006).