# Open-Access Silicon Photonics: Current Status and Emerging Initiatives

Abdul Rahim, Thijs Spuesens, Roel Baets, Fellow, IEEE, Wim Bogaerts SM, IEEE

Abstract—Silicon Photonics is widely acknowledged as a game-changing technology, driven by the needs of datacom and telecom. Silicon Photonics builds on highly capital-intensive manufacturing infrastructure, and mature open-access silicon photonics platforms are translating the technology from research fabs to industrial manufacturing levels. To meet the current market demands for silicon photonics manufacturing, a variety of open-access platforms is offered by CMOS pilot lines, R&D institutes and commercial foundries. This paper presents an overview of existing and upcoming commercial and non-commercial open-access silicon photonics technology platforms. We also discuss the diversity in these open-access platforms and their key differentiators.

*Index Terms*—CMOS, foundry, multi-project wafer (MPW), open-access, photonic integrated circuits, photonic manufacturing, silicon photonics.

#### I. INTRODUCTION

TILICON Photonics is a technology that implements highdensity photonic integrated circuits (PIC) with complex functionality using process technology of a CMOS electronics fab. Leveraging the existing CMOS infrastructure makes silicon photonics very well positioned to fabricate low cost, high yield, small form-factor and low power PICs, and at the same time scale to large commercial volumes [1]–[3]. The above definition of silicon photonics holds for a variety of material systems. To name a few, this includes different types of Silicon-on-Insulator (SOI), Silicon Nitride-on-Insulator (SiN), Germanium-on-Insulator (GOI), Germanium-on-Silicon, Germanium-on-SOI, Germanium-on-Silicon Nitride and Silicon-on-Silicon Nitrideon-Silicon. Since all these material systems can use wellestablished CMOS processing methodologies and infrastructure for densely integrated PICs, they can be considered as different flavors of silicon photonics. But to date the SOI platform is the most prominent of these material systems both in terms of technological maturity and commercial use.

The last decade has seen the transformation of silicon photonics from a promising research field to a commercial success, mainly driven by the needs for large volumes of high-speed links for datacenters, metro communication and telecommunication. However, the first conceived applications of silicon photonics were for sensing applications such as fiber gyroscopes [4]. Nevertheless, *variable optical attenuators*

Abdul Rahim, Thijs Spuesens, Roel Baets and Wim Bogaerts are with the Photonics Research Group, Department of Information Technology, Ghent University - imec and Center for Nano- and Biophotonics, Ghent University, Ghent B-9000, Belgium (e-mail: abdul.rahim@ugent.be, thijs.spuesens@ugent.be, roel.baets@ugent.be, wim.bogaerts@ugent.be). Roel Baets and Abdul Rahim coordinate ePIXfab, the European Silicon Photonics alliance.

Manuscript received May 22, 2018; revised August xx, 20xx.

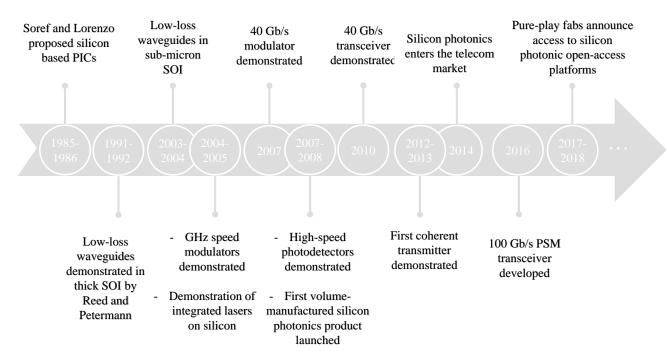

(VOA) for passive optical networks (PON), developed and commercialized by Bookham Technologies in 1997 (with the technology later taken up by Kotura and afterwards by Mellanox) were one of the first silicon photonics products to be actually commercialized [4]. Building up to the dotcom boom (and subsequent bust) in the early 2000s, silicon photonics was being considered as a technology that could address the demands of emerging tele/data communication applications. The bursting of the dot-com bubble did little to reduce that expectation, but had an obvious negative effect on the investment climate for silicon photonics. It is only in 2007 that we see transceivers for datacenter communication, developed by Luxtera, to appear on the market and become a volume-manufactured silicon photonics product [5], [6]. In 2012 Cisco, which is one of the biggest networking companies, acquired silicon photonics company Lightwire and started introducing silicon photonics solutions in their products, such as CPAK® 100GBASE fiber modules. And in 2014, Acacia Communications brought silicon photonics into the commercial telecommunication market, launching coherent silicon photonics modules for intra-data center communication and long-haul DWDM links. In 2016, chip manufacturer *Intel*, which has been building its silicon photonics technology for over a decade [7], [8], launched a 100 Gb/s parallel singlemode fiber 4-lane (PSM4) transceiver for cloud and data center applications. Inphi announced in 2017 to offer inter-datacenter 100G PAM4 DWDM silicon photonics optical engine. Figure 1 summarizes some of the major technical and commercial milestones achieved in the field of silicon photonics in the last 30+ years. The milestones mentioned above and in Fig. 1 are just a few examples of the many milestones accomplished by the field of silicon photonics, too numerous to report here completely.

Over the years there has been a manifold increase in the number of fabless silicon photonics chip and system vendors serving the data center transceiver market. Consequently, in 2017 the silicon photonics transceiver market growth has outpaced the total optical transceiver market by a significant margin [9], [10]. Furthermore, the traction of the technology platforms is stimulating a diversification in the application space: extensive R&D initiatives and start-up companies worldwide are betting on silicon photonics for a wide range of applications such as sensing and bio-photonics [11]–[13], LiDAR for automotive industry [14], [15], neuromorphic computing [16]–[18], machine learning [19], [20], quantum information processing [21], [22] and many more.

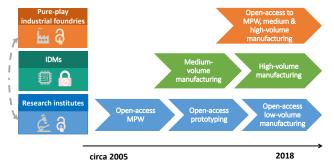

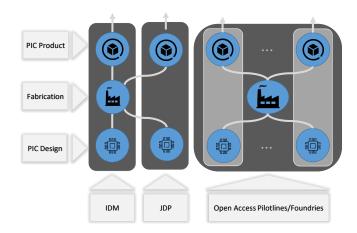

Figure 2 is showing a simplified representation of the evolution silicon photonics manufacturing has gone through

Fig. 1: Timeline of some of the major milestones in the field of silicon photonics.

in the last several years. The manufacturing process is crucial to the success of silicon photonics, but the capital investment cost for CMOS fabrication infrastructure sets a limit to the number of actors who can fabricate such devices. Similar to the ecosystem of CMOS electronics, we can identify three types of manufacturers: integrated device manufacturers (IDM) are vertically integrated and have their own infrastructure to manufacture silicon photonics chips for their own products. In stark contrast, pure-play foundries have an open-access manufacturing process, where the fabs offer PIC manufacturing services that can be used hands-off by third party external users/clients such as fabless companies. The notion "openaccess" does not mean that the manufacturing services are free of cost to the end-users, but rather that the fab imposes little or no restrictions to fabricate PICs for third parties. This is contrary to other areas of commerce where open-access implies that there is no cost to the end-users (for example, open-access publications). Anticipating a growing demand for silicon photonics PIC manufacturing, such pure-play foundries (Advanced Micro Foundry, GlobalFoundries, TowerJazz and others) have emerged in recent years to offer open-access silicon photonics technologies [23] to cater various manufacturing volumes. The third type of manufacturer is the CMOS pilot line at an advanced (public or private) research institute [24]-[32]. They offer open-access to their platforms, which includes multiproject-wafer (MPW) fabrication, and this has allowed these institutes to continuously improve their technology offering, to a point where the high technology readiness level (TRL) of their platforms has enabled them to offer low-volume manufacturing of silicon photonic chips through bilateral contracts. In some cases the R&D institute/pilot line uses the same process flow as a commercial fab to ease the transfer of manufacturing process from R&D institutes to commercial fabs. Consequently, an

entire ecosystem of companies providing PIC design support, equipment, and services for packaging, testing and assembly of PICs is very rapidly materializing, supporting fabless companies engaged in silicon photonics product development [33]–[35].

This paper gives an overview of the current status of the openaccess silicon photonics technologies and their access model. We draw parallels with the CMOS electronics ecosystem which has similar models, but for much larger manufacturing volumes. The diversity of open-access silicon photonics technologies and its impact on economy-of-scale is discussed. Recent improvements in the design methodologies for PIC design and initiatives towards high-volume manufacturing are also discussed. It is to be understood that silicon photonics is a rapidly evolving technology in a continuously changing economic landscape, implying that the specific details about the current manufacturing platforms will likely be outdated soon. However, the trends which we discuss in this paper are likely to hold for the foreseeable future. It is important to mention that the discussion presented in this paper is based solely on publicly accessible information, not only peer-reviewed articles but also information about the open-access platforms publicized by their providers.

# II. ECONOMY OF (WAFER) SCALE FOR A STANDARDIZED PLATFORM

A standardized silicon photonics platform (also termed a "generic integration platform" [36]) is one for which the manufacturing volumes are sufficiently large to establish and maintain a mature process flow. Such a platform has to offer a set of basic passive and active photonic functions, making it suitable for different applications and even for future performance scaling. This is required to offer the standardized technology as an open-access platform in a fabless model,

Fig. 2: Simplified representation of the evolution of silicon photonics open-access platforms provided by the research institutes and the pure-play fabs for different volumes of manufacturing. The evolution of the proprietary platforms developed by *integrated device manufacturers* (IDM) is also represented. It must be noted that in some cases the IDMs also provide access to their technology platforms through bilateral contracts with third-parties. The grey dashed line represents the collaboration to transfer the manufacturing process from R&D institutes to commercial pure-play fabs.

where the end-user has to adhere strictly to the process and design rules defined by the fab. These rules typically prohibit the end-user to change key platform features such as the material stack, critical dimensions, number of etch levels, doping concentrations, etc.

Leveraging existing and well-established CMOS manufacturing technology and infrastructure has catapulted silicon photonics to the forefront of photonic integration technologies. However, the manufacturing volumes needed to meet even today's largest volume applications for PICs are meager (by several orders of magnitude) when compared to the manufacturing volumes of CMOS electronics. A typical CMOS fab processes up to tens of thousands of wafers per month. In contrast, the current total silicon photonics market requires up to few tens of thousands of wafers per year [37]. Considering this disparity, it makes perfect economic sense to capitalize on existing CMOS fabs with established processes, rather than making excessive capital investments for building dedicated fab infrastructure for silicon photonics. Apart from the technological differentiators, this is one fundamental economic reason that distinguishes silicon photonics from competing PIC technologies based on III-V semiconductor, dielectrics, polymers, etc.

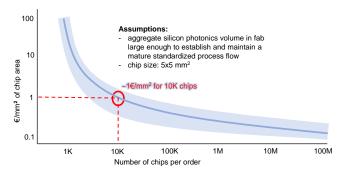

Figure 3 shows the approximate chip cost/mm² for a standardized silicon photonics technology in a CMOS fab, which is close to being fully loaded with CMOS electronics manufacturing. The cost curve is based on inputs provided by various fabs providing prototyping and/or manufacturing services for silicon photonics PICs. Here the term prototyping refers to volumes of less than 1K chips whereas volumes of less than 100K chips are classified as medium volume. It is important to highlight that the volume definitions mentioned above are valid only for PIC manufacturing as any existing volume manufacturing of PICs lies well within the low volume bracket of CMOS electronics manufacturing. The cost curve assumes a chip area of 25 mm². It accounts for the

Fig. 3: Chip cost per mm<sup>2</sup> for silicon photonics chips in a CMOS fab, shared with non-photonics use. The cost curve assumes that the silicon photonics volume in the fab is large enough to establish and maintain a mature process flow offering passive and active building blocks. Data collected from members of ePIXfab – The European Silicon Photonics Alliance (http://epixfab.eu).

infrastructure for a complete silicon photonics process flow including specific capital expenditures to set up the dedicated process for germanium growth needed for the fabrication of photodetectors in a CMOS fab.

The cost/mm<sup>2</sup> of chip area in Fig. 3 is estimated for standardized platforms supporting either monolithic or hybrid integration with electronics. Moreover, the chips considered comprise both active and passive photonic building blocks. The cost curve shows that for 10K chips, each mm<sup>2</sup> of chip area costs only 1€ (or 1\$, given that these numbers are based on order-of-magnitude calculations). This contradicts directly the gross misunderstanding that silicon photonics is viable only for very large volumes. For up to 1K chips, the cost is calculated by considering MPW fabrication, which is a cost-effective mechanism for the prototyping of a small number of PICs [38]. The fabrication cost of 10K chips is calculated by considering a full lot comprising 25 200 mm wafers (The number of chips on 300 mm wafers is roughly double, so still within the same order of magnitude). It must be noted that the cost of packaging is not considered in Fig. 3. Furthermore, it is assumed that the fabrication has a high yield due to the high maturity of the technology platform.

# III. DIFFERENT FORMS OF OPEN-ACCESS SILICON PHOTONICS PLATFORMS

As mentioned in section I there is a variety of material systems that fulfills the definition of silicon photonics, which is the ability to use existing CMOS infrastructure for the implementation of complex photonic functions and systems on a chip. In the next sub-sections, a brief description is provided for today's most prominent flavors of silicon photonics. This section only discusses those flavors of silicon photonics that are already or will be available in an open-access mode. In the current landscape, most material systems are developed for optical communication applications in C- and O-band, with wavelengths between 1300 nm and 1600 nm. Platforms for visible and mid-IR wavelengths are also developed on some of the material systems mentioned below but those developments

4

are still marginal as compared to the developments made for the telecommunication wavelength range.

## A. Silicon-on-Insulator (SOI)

Silicon-on-Insulator is the most mature silicon photonics material platform. It relies on silicon (with a high refractive index) as the waveguide core material, surrounded on all sides by a silicon dioxide (glass) cladding. This gives a 41% index contrast, which is defined as  $(n_{core}^2 - n_{clad}^2)/(2 \times n_{core}^2)$ , in the telecommunication window. SOI can again be subdivided in two classes, namely sub-micron SOI and and thick SOI. The classification of sub-micron SOI and thick SOI is based on the thickness of the silicon guiding layer (i-e, the device layer of photonic components) and not the thickness of the buried thermal oxide (BOX). For thick SOI the guiding layer is typically larger than 1  $\mu$ m whereas for sub-micron SOI the guiding layer thickness is well below 1  $\mu$ m. For both classes of SOI used in silicon photonics, the BOX layer is usually thick enough to prevent the leakage of optical signal into the substrate. Another distinction the two have is their current wafer size. Unlike thick SOI, sub-micron SOI is available in wafer size of 200 mm (8 inch) or more.

1) Sub-micron SOI: In terms of economic activity, wafer volume and number of actors in the fabrication field, submicron SOI is by far the dominant flavor of silicon photonics, and is often considered as a synonym for the entire field. Openaccess sub-micron SOI platforms provide the most complete set of passive and active integrated photonic functions including waveguides, splitters, filters, high efficiency grating based fiberchip couplers enabling wafer level testing, phase-shifters, (highspeed) modulators and (high-speed) photo-detectors. For submicron SOI platforms, the waveguide layer is typically only few hundred nanometer thick to ensure single-mode operation of the slab waveguide. The waveguide width is typically between 400 nm and 1000 nm, and the tight confinement of the optical field in a sub-micron SOI platform allows for waveguide bends of a few microns. For example, single mode strip waveguides in 220 nm SOI allow for a minimum bend radius of  $\sim 5 \mu m$ . Such a small bend radius enables dense integration of waveguide functions on sub-micron SOI platforms.

Over the years, a variety of platforms have emerged with different thickness of the guiding silicon layer [24]–[28], [30], [31], [39]–[44], all with thicknesses of a few hundred nanometer. Even with this variation, SOI with a 220 nm core thickness has become a kind of de-facto standard and it is being used by a majority of the fabs. Originally this value of silicon thickness was chosen because of its commercial availability in SOI wafers, and it provided a waveguide layer which supported exactly 1 guided slab mode for both TE and TM polarization at wavelengths between 1.5  $\mu$ m and 1.6  $\mu$ m. This helped in maintaining single-mode operation in PICs. Moreover, SOI stacks with 310 nm, 340 nm and 500 nm waveguide thickness have been adopted to facilitate laser integration on SOI [45]–[48] and explore mid-IR applications [49]–[52].

The high optical confinement of sub-micron SOI also brings along certain difficulties: the silicon waveguide devices are extremely sensitive to nanometer-scale dimensional variations [53], [54]. The consequences of this sensitivity are higher waveguide loss, backscattering [55], [56] and spectral shift in interferometric [57] and resonant devices [58], [59]. The propagation losses in sub-micron silicon waveguides can be minimized with thicker and wider waveguides. For example by using 500 nm thick SOI, waveguides losses of a few dB/m are possible to enable applications that require long delay lines, high-O resonators, narrow filters, etc. [60]. Given that every fabrication process introduces some variability at the nm-scale (inter-wafer, intra-wafer, inter-die or intra-die, both systematic and random), this variability is a fundamental challenge of the sub-micron SOI platforms [61]. However, smart design strategies have been a topic of active research to make fabrication tolerant sub-micron SOI PICs [62], [63]. Another consequence of the high optical confinement in sub-micron SOI waveguides is the onset of two photon absorption (TPA) at power levels of few tens of mW and higher. TPA not only introduces non-linear propagation losses in sub-micron SOI waveguides but also leads to free carrier absorption (FCA) induced loss and index change. Beyond wavelengths larger than 2.2  $\mu$ m, the effect of TPA is drastically reduced [64]. This makes sub-micron SOI structures ideal for implementing non-linear optical devices at these longer wavelengths [49], [65], [66].

2) Thick SOI: For the so-called thick SOI platforms, the waveguide layer is typically thicker than 1  $\mu$ m. Silicon photonics started with the demonstration of low loss waveguides on thick SOI platforms [67]–[69]. Importantly, this platform offered one of the first and the longest lasting silicon photonics product in the form of a VOA for PONs [4].

The single mode condition for thick SOIs waveguides is only met for rib-waveguides with a specific aspect ratio of waveguide width and height [69]. Slab and strip waveguides in thick SOI are invariably multimode (at least at telecommunication wavelengths), but it is possible to keep light in their fundamental mode using adiabatic rib-strip conversion structures [70]. The larger mode field leads to increased optical confinement inside the Si core, making thick SOI waveguides less sensitive to dimensional variation, surface roughness and polarization [71], [72]. It also allows them to handle much higher optical power (even >1 W) before nonlinear effects kick in, and to extend the operating wavelength to the mid-IR [75]. Thick SOI waveguides generally have low propagation losses (~0.1 dB/cm) and weak backscattering, making them especially suitable for high performance passive functionalities [29], [74]. The most common SOI thickness is 3  $\mu$ m, which is also available in open-access [73].

Due to their weak lateral index contrast, the bend radius for rib waveguides in thick SOI is in the mm-scale, which doesn't support dense integration. Therefore, *total internal reflection* (TIR) mirrors [76] and *Euler bends* in multimode strip waveguides [77] have mostly replaced rib waveguide bends in thick SOI. With them, the typical bend radius in thick SOI is now ranging from 1 to 50  $\mu$ m [77], which makes also thick SOI suitable for very dense integration. The Euler bends have very low loss for both polarizations (<0.1 dB/bend even for a few  $\mu$ m radius) and have enabled implementation of polarization independent devices with compact footprint for optical commu-

nication [78] and microwave photonics applications [79]. Unlike sub-micron SOI, where high-speed modulation and detection functions are monolithically integrated, open-access thick SOI platforms typically rely on flip-chip-like integration to provide these functions [80]. Nevertheless, low speed modulation of optical signals in the kHz and MHz range is available in open-access thick SOI platforms [29], [81]. High-speed modulators and photodetectors have been reported using thick SOI in [82]–[84] but they are currently not offered by open-access platforms. Input and output coupling for thick SOI waveguides is typically implemented via end-fire coupling or up-reflecting mirrors.

The main limitations in thick SOI technology relate to the large topography of the wafers. This makes it more difficult to realize high-speed active components, to precisely control the waveguide dimensions and to use high-resolution lithography for narrow waveguide features. Due to the high topography, thick SOI PICs are typically fabricated in older generations of CMOS electronics fabs or in MEMS fabs, rather than state-of-the-art CMOS fabs.

# B. Monolithic silicon photonics-electronics co-integration

Due to the potential compatibility of silicon photonics with the well-established industrialization methodologies used in CMOS technologies, there has been a significant thrust for monolithic integration of silicon photonics with electronics [85]. The additional parasitic capacitance and inductance of wirebonds or micro-bumps used by the hybrid *electronic-photonic integrated circuit* (EPIC) platforms [86]–[89] is minimized by *Front-end-of-line* (FEOL) integration of photonic components with electronics [30], [90]. Monolithic EPICs have a potential to meet the stringent power dissipation and aggregate throughput demands for short-to-long-range photonic interconnects [30], [44], [90].

Various demonstrations of monolithic EPICs have been reported [5], [27], [30], [41], [44], [91]–[96]. These implementations are carried out on different types of material platforms such as on bulk CMOS wafers [41], [91], sub-100 nm SOI [30], [44], [93] and 220 nm SOI platforms [27]. Moreover, various technology nodes such as 90 nm CMOS [94], 65 nm CMOS [92], 45 nm CMOS [93], 28 nm CMOS [97] and 250 nm BiCMOS [96], [98] are used for the implementation of monolithic EPICs.

These solutions can be categorized into two approaches. In one approach the transistor process development is completely decoupled from the photonic process development. This approach provides the opportunity to optimize the performance of photonic building blocks as reported in [5], [44], [91], [94] where bulk CMOS or sub-100 nm SOI platforms are used. As an example, the sub-100 nm SOI platform demonstrated in [44], [94] provides passive and active functions in the C-band. Similarly, on bulk CMOS platform, in [41], [91], [97] photonic functions are defined on the poly-crystalline silicon layer grown on the locally thicker silicon oxide isolation trenches of the transistor. This platform provides tight bending radius for waveguides and the optical propagation loss in the O-band is  $\sim 20$  dB when both active and passive devices where

defined on the same wafer. An implementation on 220 nm SOI platform where optical device modules were inserted in the baseline BiCMOS flow are reported in [27]. In this approach bulk silicon regions on the SOI substrate are defined for the monolithic integration of high-speed electronics and photonics using 250 nm BiCMOS technology.

The second approach does not deploy any change in the existing CMOS electronics process flow to demonstrate photonics functions. This approach is also known as "Zerochange" silicon photonics [30], [93] and typically uses a sub-100 nm SOI platform. As an example, in [30] such a "Zero-change" silicon photonics platform is demonstrated on a partially depleted SOI providing active and passive photonics functionality with tight bending radius and low waveguide loss for the C-band after locally removing the silicon substrate under the buried oxide layer, which is not thick enough to prevent optical leakage into the substrate.

#### C. Silicon Nitride

The lower wavelength limit of SOI transparency is  $< 1.1 \mu m$ , corresponding to the bandgap of silicon. This implies that SOI is not a viable material system for applications operating at visible and very-near-infrared wavelengths. However, inspired by the success of SOI, there has been a growing interest in recent years to extend the wavelength range of "silicon photonics" to the visible domain using *silicon nitride* (SiN) as a waveguide material. SiN-based silicon photonics [99]–[102] has a transparency window that goes from  $\sim 0.4 \ \mu m$  all the way up to mid-IR wavelengths of 4  $\mu$ m. SiN technologies can be categorized on the basis of the deposition method used (PECVD and LPCVD) [100], [103], [104], [106]-[110]. The PECVD platforms exhibit higher waveguide losses at the 1.55  $\mu$ m telecommunication band but do not require processing steps at temperature beyond  $450^{\circ}$ C, which is an asset for certain process flows and applications. For applications operating at 1.55  $\mu$ m LPCVD-SiN is typically used. Because there is no TPA in SiN, much higher power densities than in submicron SOI can be supported, and the lower loss waveguides (with lower phase errors) make it easier to create high-quality filter circuits [111], [112].

SiN provides moderately high index contrast, which is 3.5 to 4.5 times less than that of sub-micron SOI in the telecommunication window. This leads to reduced loss and an order of magnitude weaker back-scattering for the SiNbased waveguides [101], [113]. As compared to sub-micron SOI platforms, SiN has  $\sim$ 5 times lower temperature sensitivity [101]. This means that SiN is a better suited platform for applications in which the temperature sensitivity may be an issue, but where active temperature control is not desirable. At the same time, the low temperature sensitivity of SiN leads to a higher power dissipation for tunable devices using the thermo-optic effect. Similar to SOI, we can identify trends towards thin and thick SiN core layers. Typically thick SiN layers are exploited to develop high-power silicon photonics PICs [114]. This diversity of layer thickness is enabled by the flexible PECVD or LPCVD process used for the deposition of SiN layers. This contrasts with the SOI case, where the SOI

wafer provider will only manufacture wafers of a specific layer thickness if there is a sufficient demand for it.

## D. Germanium based silicon photonics

220 nm SOI with 2  $\mu$ m BOX has a transparency of up to 2.9  $\mu$ m [115] whereas this transparency reaches 3.8  $\mu$ m for SOI with 400 nm guiding silicon layer thickness [50], [116], [117]. For the former, the transparency is limited by the substrate leakage while for the latter, the transparency is limited due to the onset of absorption in the buried oxide layer of SOI. Approaches such as the implementation of suspended SOI strip and slot waveguides are developed to extend the transparency range further into the mid-IR wavelengths [118]–[121].

Germanium-on-silicon (GOS) provides a moderate-vertical-contrast waveguide system with a transparency window in the mid-IR range of 2  $\mu$ m to 8  $\mu$ m [117], [122]–[125]. Though Germanium itself is transparent up to ~14  $\mu$ m, the silicon cladding starts absorbing at ~8  $\mu$ m and beyond. This makes it a suitable silicon photonics material systems for on-chip spectroscopic systems for gas and liquid sensing, monitoring of air or oil quality, control of engine emissions, free-space communication and light detection and ranging (LiDAR) systems [117], [122], [126]. Apart from GOS, there has been a variety of other Germanium-based mid-infrared technology platforms such as Germanium-on-SOI [127]–[129], Germanium-on-Silicon Nitride [130], Si<sub>(1-x)</sub>Ge<sub>x</sub>-on-Silicon [131] and suspended Germanium [132], [133].

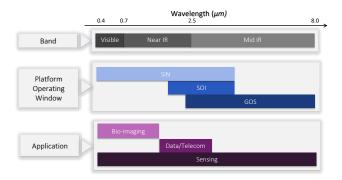

Figure 4 gives an overview of the various single-mode waveguide cross-sections possible with the different flavours of silicon photonics platforms discussed above. The sub-micron SOI and SiN platforms support fully etched strip waveguides, deep and shallow etched rib waveguides, and slot waveguides. Specialized geometries for waveguides such as Box-shell are also available in SiN-based silicon photonics [104]. Both sub-micron SOI and SiN material systems support different types of claddings (i-e, air and oxide). Thick SOI supports only rib waveguides with different cladding types, whereas germanium-based mid-infrared platforms typically support air-cladded waveguides of strip, rib and slot types. Fig. 5 shows the transparency range of SOI, SiN and GOS material systems and the corresponding applications linked to optical transparency windows of these material systems.

#### E. Need for standardization in silicon photonics

Each fab requires to develop a standardized technology with an established and mature process flow to provide manufacturing of silicon photonics PICs. If more fabs adopt the same standard, fabless companies will have more supplier options, which reduces the costs and the risks for the silicon PIC design. However, in the current landscape of silicon photonics technologies, there is no single standard technology. Rather, each fab has defined its own standard technology. This helps them to maintain fewer processes, which results in reduced cost for a foundry.

Due to the high index contrast of the material system, dimensional control is important [31], [54], [57]. For example, the process control in terms of waveguide width and

| Waveguide<br>Type | Single Mode<br>Waveguide Cross-<br>sections | Sub-<br>micron SOI |   |   | Ge-based mid-<br>infrared material<br>systems |  |

|-------------------|---------------------------------------------|--------------------|---|---|-----------------------------------------------|--|

| Strip             | Air                                         | ✓                  | × | ✓ | ✓                                             |  |

|                   |                                             | ✓                  | × | ✓ | ×                                             |  |

| Rib               | Air                                         | ✓                  | ✓ | ✓ | ✓                                             |  |

|                   |                                             | ✓                  | ✓ | ✓ | ×                                             |  |

| Slot              | Air                                         | ✓                  | × | ✓ | ✓                                             |  |

| Box-shell         |                                             | ×                  | × | ✓ | ×                                             |  |

Fig. 4: Typical cross-sections of single-mode waveguides supported by the different variants of silicon photonics platforms. In many cases the air cladding is replaced by a silica cladding, which creates a less fragile waveguide (less susceptible to dust).

Fig. 5: Different forms of silicon photonics operating from visible to mid-IR wavelengths to provide integrated photonics solutions for bio-imaging, optical communication and sensing.

height required for wavelength selective devices in sub-micron SOI devices is more stringent than for CMOS electronics. Standardization in the process flow provides stability and repeatability in the device performance for large manufacturing volumes. Moreover, it helps in gauging variance in key device performance parameters [24], [31]. A well-understood and stable device performance is crucial to develop complex photonic integrated systems on a chip.

#### F. Value of diversity in silicon photonics

A single standardized technology platform is not necessarily capable of addressing the requirements for various applications in the very wide range of market sectors where PIC technology can potentially bring new value [134]. This means that, while standardization is a must for the above-mentioned technical and economic reasons, so is the diversification. This is not something that is unique to silicon photonics. Again, we can draw the comparison with electronics, where CMOS is the most dominant technology, but which comes in a variety of nodes with different performance and price points. On top of that there is diversity for targeting specialized markets such as high-power electronics, ultra-high frequency RF electronics, ionization radiation resistant (rad-hard) electronics, etc.

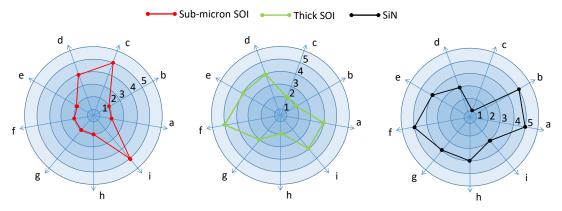

(a) Propagation Loss, (b) Layer Stack Flexibility, (c) Active Functions, (d) Efficient IO, (e) Back-scattering, (f) High power operation, (g) Transparency, (h) Thermal sensitivity, (i) Bend Radius

Fig. 6: Qualitative representation of the current status of sub-micron SOI (in red), thick SOI (in green) and SiN (in black) on a scale of 1 to 5 (5 is better). Sub-micron SOI complements SiN in providing compact form factor PICs through its small bending radius, high-efficiency IO by using grating/edge couplers and active functionalities such as high-speed photodiodes and detectors. On the other hand, SiN provides low loss waveguides, broad transparency window for visible, NIR and midIR applications, ability to deal with 100s of mW CW power and reduced back-scattering due to its lower index contrast than SOI. Thick SOI is known to provide lower propagation loss, lower back-scattering, and high power operation but does not provide high-speed active functionalities.

The degree of material diversity in silicon photonics enables a situation where technology platforms complement one another. Such a diversity not only prevents monopoly of one technology platform but also develops a sense of competition between technologies and makes them agile for evolution. As an example, Fig. 6 provides a qualitative comparison of sub-micron SOI (left), thick SOI (middle) and SiN-based (right) silicon photonics platforms. One can observe the complementarity of SiN (right plot of Fig. 6) and sub-micron SOI (red lines in left plot of Fig. 6). SOI complements SiN by providing compact form factor PICs through its small bending radius, highefficiency fiber-chip coupling by using grating/edge couplers and active functionalities such as high-speed photodiodes and detectors. On the other hand, SiN provides lower loss waveguides, broad transparency window for visible, NIR and mid-IR applications, ability to deal with 100s of mW CW power and reduced back-scattering due to its lower index contrast than SOI.

Table I lists the type of material stacks used by various openaccess silicon photonics technologies and their key technical differentiators. Moreover, it is also possible to combine elements of different platforms together. The manufacturing flexibility of SiN layers makes it possible to integrate SiN layers into the SOI platforms [108], [135]–[139]. In such a platform, passive components demanding low loss and high fabrication tolerance are defined on the SiN layer [140], [141]. Functions such as modulators and photodiodes are then defined in the Si layer.

Along with the platform diversity there is a diversity in infrastructure needed for silicon photonics. Most of the submicron SOI platforms use 200 mm or 300 mm wafers. For NIR applications on sub-micron SOI, the desired feature sizes or *critical dimensions* (CD) can be delivered by 130 nm or

90 nm CMOS pilot lines and foundries. However, due to the high index contrast of sub-micron SOI, the required accuracy corresponds more to a 40 nm or 65 nm CMOS technology node. These nodes already make use of the high-end 300 mm manufacturing equipment such as immersion lithography, do not yet require expensive techniques such as double/triple patterning. Still, the processing cost on 300 mm wafers at these nodes is considerably higher than that of older CMOS nodes on 200 mm wafers. Yet, for mid-infrared PICs the scaling with wavelength – of photonic structures to larger dimensions relaxes the fabrication tolerances for sub-micron SOI and GOS based PICs. Due to the relaxed tolerances of moderate index contrast material systems (i-e, SiN, GOS), the platforms on these material systems demand less advanced lithography and etching infrastructure, making them more cost-effective in certain volume manufacturing cases. As a result, wafer sizes of 100 mm, 150 mm, and 200 mm are still prevalent today for these platforms.

In the current landscape of open-access technologies, there is clear scope for a moderate number of diversified platforms. The sustainability of these platforms depends on whether there is sufficient market for each platform. Therefore there is a "sweet spot" in terms of standardization and diversity. It is still an open question how this sweet spot will evolve and which silicon photonics platforms will prove to be sustainable.

# IV. THE SILICON PHOTONICS OPEN-ACCESS MODEL

# A. Access Models

One of the key mechanisms behind the economic success of silicon electronics is the open-access model, where fabless companies can have chips fabricated in commercial foundries that provide standardized fabrication platforms. This separation of design and product development on one hand, and fabrication on the other hand, has acted as a multiplier in economic activity, with hundreds of thriving fabless companies for every foundry [34], [142], [143]. It is a win-win formula, lowering the investment for fabless companies and generating profitable volumes for the foundries. In the silicon electronics ecosystem, the open-access foundry model can perfectly coexist with vertically integrated IDMs that benefit from a tight integration of product know-how and their own proprietary fabrication processes.

Given the many parallels between silicon photonics and silicon electronics, the open-access foundry model (or *fabless* model) can stimulate a similar growth in fabless PIC-based product development. Open-access is a model that offers fabrication services to third parties i.e. to external users /clients outside a technology consortium. open-access is facilitated through an eco-system providing appropriate support services and tools such as design software, packaging, and testing [34], [144]–[146].

Open-access is not the only possible access model to fabrication technology. We already mentioned IDMs with vertically integrated fabrication and product development, but it is also possible for fabless companies to access foundry capabilities on a bilateral or multilateral basis, co-developing proprietary flavors of a foundry's technology platform. This is a model that has yielded some of the most visible successes in silicon photonics [37], [38], [90], [147]. These are models that we also find in electronics and other custom semiconductor platforms such as *micro-electromechanical systems* (MEMS). Fig. 7 gives a schematic representation of different access models for PIC-based product development.

Given that a fabless/foundry ecosystem should address the largest possible application space, the versatility of silicon photonics open-access technology platforms and the ease of their access is of paramount importance. This allows fabless companies to develop innovative products and evolve seamlessly from prototyping to small-volume manufacturing and possibly all the way to high volume manufacturing [142]. Like in electronics, this will also require a certain diversity in the technology offerings, allowing product developers to pick the platform best suited for their application.

# B. Open-Access Workflow

In an open-access model, it is important for all parties involved that fabless companies find their way to a suitable foundry as easily and as affordably as possible. For electronics, this was given a boost through the creation of the multi-project-wafer service *MOSIS* in 1981 [23], [34], [144]–[146],later mirrored by Europractice IC in Europe [148]. For silicon photonics, ePIXfab – a joint initiative by *imec* (Belgium) and *CEA-LETI* (France), operated from *Ghent University* (Belgium) – pioneered a similar access mechanism for silicon photonics through MPW service since 2006. By 2011, the open-access silicon photonics technologies of *IHP* and *VTT* were also

Fig. 7: Schematic representation of three prominent access models for PIC manufacturing. The first column represents vertically integrated IDMs. They internally control the entire process from chip design to production. Fabless companies can have *joint development programs* (JDPs) with IDMs as represented in the second column. The third column shows different end-users submitting their PIC designs to openaccess silicon photonics pilot lines/foundries for their product development.

offered by ePIXfab.1

A similar initiative, named Optoelectronic Systems Integration in Silicon (OpSIS), was launched in 2010 from University of Washington and University of Delaware [38]. While the initiative did not sustain beyond 2015 it was vividly successful in providing design support for researchers in silicon photonics and organization of multiple MPW runs through fabs such as BAE Systems CMOS fab and Institute of Microelectronics (IME) in Singapore [37], [38]. Recently, a new initiative called the American Institute for Manufacturing integrated Photonics (AIM Photonics) has emerged. It is currently engaged in establishing an ecosystem supporting the complete silicon photonics product development (from design to prototype to pilot or mid-scale wafer and package manufacturing) using the 300 mm fab at the State University of New York (SUNY) Polytechnic Institute and packaging facilities in Rochester, New York [149], [150].

Various other initiatives, which provide open-access silicon photonics technologies to end-users have also emerged. For example, *Photonics Electronics Technology Research Association* (PETRA) in Japan and *Electronics & Telecommunications Research Institute* (ETRI) in Korea provide access to the end-users in these respective countries. Similarly, other countries have developed open-access technologies to address the demands of local and/or global end-users.

When an end-user wants to access PIC fabrication technology, the first challenge is to determine if silicon photonics technol-

<sup>1</sup>Since 2015, the MPW services offered by *ePIXfab* have been transferred to *Europractice IC* Service. *ePIXfab* has transformed itself into the *European Silicon Photonics Alliance*, with the majority of the European open-access silicon photonics fabs as its members, and continues to promote silicon photonics science, technology, and application through fabless models (http://epixfab.eu).

ogy will meet the system specification and which technology flavors from a diverse pool of foundries are the most suitable. In many cases, an end-user product developer does not have the internal technical know-how to make this platform selection, let alone kick-start the design of a full-custom complex PIC. As with custom electronics, this creates a space for photonic design houses and brokers that can support the end-user in his choice of technology.

After the selection of technology, the open-access process makes it possible to get started on a practical design without the need for complex bilateral discussions. Open-access foundries provide access to process design kits (PDK) after signing a standard design kit license agreement (DKLA) with the fab. In a case where the PIC design is outsourced to a design house, a similar non-disclosure agreement (NDA) is usually signed with the design house.

The PDK provided by the foundry is the interface between the designer and the technology [151], [152]. It contains sufficient technical details of the technology to enable the designer to create either full-custom layouts or custom circuits. A PDK is typically compatible with specific design tools and is always foundry-specific. Unlike with electronics, where there is some standardization of the content of PDKs, there is as yet no standardized blueprint for photonics PDKs. In its simplest form, it contains layer description associated with a process step and critical dimensions that define the design rules for the process steps. More advanced versions of PDKs also contain:

- Component libraries with their parametric cells and their layouts (either actual layouts or IP-protected black-boxes)

- Technology handbooks describing different technology steps and process variability statistics, design rule manual and component library handbook providing statistics about their performance

- Design rules enabling the designer to match the critical dimensions and density of the design with the capabilities of the fab concerning mask preparation, lithography and chemical-mechanical polishing. These design rules are often embedded in a deck for design rule checking (DRC) software.

Recently fabs and design tool developers have started codeveloping calibrated *compact model libraries* (CML) for the PDKs of their respective open-access technologies. The CML is meant to improve the accuracy and reliability of PIC designs by enabling the designers to accurately simulate and optimize the performance of complex PIC designs before fabrication [153], [154]. In the future, such CMLs will be an integral part of PDKs. Furthermore, the fabs have also been striving to include 3-D capable *layout-vs-schematic* (LVS) checking and the capability to run co-simulation with electronics ICs [61].

## C. Open-Access Modalities

Generic open-access technologies are available in different modalities, depending on the phase of the product development:

- Multi-project wafer (MPW),

- Dedicated engineering runs,

- · Pre-production, low and high volume manufacturing.

For the proof-of-concept and early stage R&D, MPW shuttle runs are ideally suited. MPWs play an instrumental role in catalyzing the field of silicon photonics by providing lowcost access to start-ups, small/medium enterprises (SME), and low-CAP companies to test their design ideas using a standard process flow of different fabs offering open-access technologies [33], [34], [143]. MPW helps the designers to gauge the capabilities available in a technology. In MPWs, several users share the design area and share the mask and fabrication cost. Typical design sizes for each user consume few tens of mm<sup>2</sup> with a typical cost of a few k€ for passive PICs to a few tens of k€ for PICs with advanced functionalities of modulation and photo-detection [148]. In this stage, the end-user typically receives few dozens of chips. The designer has the freedom to make the design using custom components from his own component library and a component library of the fab PDK. The intellectual property (IP) of the user is preserved by ensuring that the designs of the user are not visible to any other user sharing the same design reticle.

In many cases, the fab provides access to MPW prototyping services through a technology broker. Due to the very low-volume nature of the MPW service, fabs collaborate with technology brokers who aggregate the designs of the end-users. Moreover, they support the end-users by providing access to PDK for the fab, relevant design tools, and undertake layout verification by *design rule checking* (DRC). A technology broker can provide support for multiple technology platforms from different foundries. Table I lists some of the most prominent open-access silicon photonics platforms offered by various CMOS pilot-lines, research institutes and industrial fabs.

On average each foundry offering MPW shuttles provides three to six runs in a year. In most cases, the MPW access is provided by research fabs. These fabs typically have a long fabrication cycle due to the limited capacity of their infrastructure. Typically, the turn-around time for a design with full process flow (e.g., passives and actives) takes 9-12 months. If the design has only passive devices, then this time is typically 4-6 months. These long production cycles prohibit the rapidlearning desirable during the early research, development and prototyping phase of the product development. To circumvent this very issue, rapid prototyping services for silicon photonics have emerged. In some cases, these prototyping services are compatible in terms of processes, specifications, design flow and design rules with the technology offered by an MPW fab. The typical turn-around time for a rapid prototyping service is few weeks whereby an end-user gets one to ten chips by paying a cost comparable to an MPW run through a fab. Most rapid prototyping platforms provide passive functions only, but in a few cases, they offer the complete process flow comprising both active and passive functions. Table I lists the few prominent platforms available in rapid-prototyping mode.

Typically 50-70 % of end-user designs in an MPW are based on user-defined custom building blocks [151]. Before moving to early prototype dedicated production runs, typically an end-user requires multiple tape-out iterations to optimize custom-designed building blocks and reach the performance specifications. This cycle of design optimization is not only

TABLE I: Prominent open-access silicon photonics technology platforms offered by various fabs, their technology and access mechanism.

| Foundry            | Platform        | Technology                | Access              | Waveguide Layer<br>Thickness<br>(nm) | Wafer Size<br>(inch) |

|--------------------|-----------------|---------------------------|---------------------|--------------------------------------|----------------------|

|                    |                 | RAPID PROTOTYPIN          | IG SERVICES         |                                      |                      |

| AMO                | thin SOI<br>SiN | e-beam                    | Direct              | 220, 340                             | 6                    |

| Applied Nano Tool  | thin SOI        | e-beam                    | Direct              | 220, 300                             | 6                    |

| CNM/VLC            | SiN             | e-beam                    | Direct              | 300                                  | 4                    |

| Cornerstone        | thin SOI        | 248 nm                    | Direct              | 220, 340, 500                        | 8                    |

| LIGENTEC           | SiN             | -                         | Direct              | up to 2500                           | 4/6                  |

|                    |                 | CMOS PILOT LINES & RES    | EARCH INSTITUTES    | •                                    |                      |

| AIM (SUNY)         | thin SOI        | -                         | MOSIS               | -                                    | 12                   |

|                    | SiN             | -                         |                     | -                                    | 12                   |

| CEA-LETI           | thin SOI        | 193 nm                    | CMP                 | 310                                  | 8                    |

|                    | Ge/SiGe         |                           |                     | up to 3000                           | 8                    |

| IHP                | SiGe BiCMOS     | 248 nm                    | Europractice        | 220                                  | 8                    |

| IMEC               | thin SOI        | 102                       | Europractice        | 220                                  | 8                    |

|                    | SiN             | 193 nm                    | Direct              |                                      | 8                    |

| IMECAS             | thin SOI        | -                         | SPP                 | 220                                  | 8                    |

| INPHOTEC           | thin SOI        | e-beam                    | Direct              | 220                                  | 6/8                  |

| Sandia Lab         | thin SOI        | -                         | Direct              | 240                                  |                      |

| VTT                | thick SOI       | UV                        | Direct              | 3000                                 | 6                    |

|                    |                 | INDUSTRIAL                | FABS                |                                      |                      |

|                    | thin SOI        |                           |                     | 220, 340                             | 8                    |

| AMF(former IME)    | SiN             | 248/193 nm                | Direct <sup>†</sup> | -                                    | 8                    |

| ,                  | SiN-on-SOI      |                           |                     | -                                    | 8                    |

| CompoundTek        | thin SOI        | 193 nm immersion          | Direct              | -                                    | -                    |

| Global Foundry/IBM | thin SOI        | 193 nm immersion / 248 nm | MOSIS, Direct, TAPO | sub-100 nm                           | 8/12                 |

| SilTerra           | thin SOI        | -                         | Direct              | -                                    | 8                    |

| SMIC               | Thin SOI        | _                         | Direct              | 340                                  | 8                    |

| ST Micro§          | thin SOI        | 193 nm                    | Direct              | 310                                  | 12                   |

| TowerJazz          | thin SOI        | 193 nm                    | Direct              | -                                    | 8                    |

| TSMC               | thin SOI        | -                         | _                   | _                                    | 12                   |

| LioniX             | SiN             | UV                        | Direct              | flexible                             | -                    |

†CMC Microsystems (Canada) brokers MPW services to Canadian universities and industries. §ST Micro platforms is accessible via bilateral contracts

time consuming but also has a significant economic cost. An alternative is to go for a dedicated engineering run directly. In such tape-outs, the same process flow as for MPW shuttles is used, but a user can get more wafers and more design space. While expensive, they provide the end-users with an opportunity to put large custom building block design sweeps to optimize the overall PIC design with potentially fewer iterations.

Silicon photonics technology accessible via MPW has a fixed process flow with typically a high level of maturity (TRL level 6 and beyond). The platform is generic in the sense that slight variants of the same process flow may be used for diverse applications. Despite the generic nature of open-access technology, in many cases this process flow is incapable of delivering the desired performance specifications. Also, when moving from R&D to commercialization, a generic platform might still fall short of the functional performance specifications of a PIC through design optimization only. Both cases demand a customized process flow, which may involve new process development through dedicated engineering runs. Various iterations are carried out to achieve maturity for the customized processes, which makes the turn-around time of such dedicated engineering runs longer than is the case with MPW. The end-users are provided with a customized PDK with agreement on the design-rules and design layers making these runs more flexible. Typically a customized dedicated

engineering run costs 10× more than an MPW participation.

Once the PIC design has reached a certain maturity, the silicon photonics product development requires pre-production engineering runs. During these runs, the process repeatability is established to ensure a predictable process flow. During this phase, corner lots are run as a critical validation step to determine the worst-case estimate of the system functional performance specification. Such lots are important for defining the ideal process conditions for low or high-volume manufacturing. Manufacturing volumes of a few hundreds to a few thousands of wafers per year are considered to be lowvolume for PIC manufacturing. As today most open-access technologies are offered by R&D fabs, this is the only volume bracket that can be addressed, as these R&D fabs generally do not have a capacity for medium- or high-volume production. However, R&D fabs may have agreements where the endusers can translate the process developed in a R&D lab to commercial fabs providing medium- and high-volume manufacturing. This process transfer requires matched geometries (i-e, minimum feature size), a similar performance of building blocks including the performance variability, matched PDK and associated device models, and migration of other parts of the supply chain (e.g., assembly). ST Microelectronics, though an IDM, is one of the first foundries to provide access to its technology platform for volume manufacturing through

bilateral contracts [147]. Other foundries with the capacity for high-volume manufacturing such as *GlobalFoundries* and *TowerJazz* have also announced to launch open-access silicon photonics platforms. Moreover, in 2017, *TSMC* developed a *through-silicon-via* (TSV)-enabled silicon photonics platform in a 300 mm foundry. This platform has demonstrated state-of-the-art performance for various passive and active building blocks [90].

Table I provides a non-exhaustive list of institutes and foundries providing (or in the process of providing) open-access silicon photonics technologies. In the early days, the fabs chose 220 nm SOI as the substrate for their platform development [24], [25], [27], [31], [41]. More recently silicon photonics open-access platforms based on 310 nm SOI [26], [40], 500 nm SOI [155], SiN and Germanium-based mid-infrared platforms have also emerged. The technology, access mechanism and wafer size used are also listed in Table. I. The table will likely evolve considerably in the next years.

# D. Recent Open-Access Silicon Photonics Technology and Ecosystem Developments

1) Process technology: Advances in process technologies for silicon photonics platforms has resulted in their improved performance. These improvements resulted in demonstrating passive devices with lower loss, superior spectral accuracy and higher reproducibility. Performance of active devices has also benefited from the evolved processing technology whereby different types of efficient modulators and photo-detectors operating at high-speed are demonstrated [24]–[28], [31], [32], [156]–[161]. As a result of advances in the process technology, open-access fabs have consolidated their platforms by offering new process modules such as very low loss waveguides [156], [157], high-speed modulators [162]–[167], integration of efficient electro-optic materials in a silicon photonics process flow [174], [175], multi-layer SiN on Si [108], [135]–[139], and broadband fiber-chip-fiber couplers [168]–[173], [176].

Most applications of PICs require that a light source supply the chip with either a clean optical carrier (laser) or broadband light. A variety of approaches are pursued to bring III-V and SOI-based silicon photonics together [177]-[179]. Demonstrations are reported to reach the ultimate solution of a monolithically integrated quantum-well or quantum-dot III-V laser source in Silicon Photonics [180]–[186]. Currently, the most mature solutions are provided by hybrid or heterogeneously integration of quantum well or quantum dot laser source with silicon photonics PICs [184], [187]-[189]. Openaccess platforms are actively engaged in developing the waferscale integration of light-sources on silicon PICs. Wafer-scale integration is required to preserve the cost advantage of silicon photonics. A recent demonstration of wafer-scale heterogeneous integration of light-sources is reported in [190]. An incumbent technology that can provide wafer-scale integrated laser sources is micro-transfer-printing ( $\mu$ TP) [191]. Other open-access technology consortia such as AIM Photonics are also exploring the development of integrated laser solutions including quantum dot based wafer-scale epitaxially grown laser sources within their silicon photonics technology platform [149], [150].

To gauge the process stability and capability of the PIC platforms offered by the open-access fabs, methodologies and infrastructure for platform performance tracking are developed by monitoring the key dimensions for each processing step [24], [192]–[194]. Furthermore, infrastructure for wafer-scale end-of-line optical, electro-optic and electrical testing using automatic setups is set up to determine device performance [31], [90], [195].

2) Design Tools: Open-access technologys only make sense in combination with a design infrastructure which enables platform users to design their own devices and structures. We can identify two essential parts of the design infrastructure: design/simulation tools and process design kits (PDK). A number of design tools for photonic integrated circuits have emerged in the past two decades [152]. At first, they supported the designer in generating complex layout features for photonic components, which are often much more complicated than those for electronics. Photonics requires curvilinear waveguides and custom all-angle geometries, while typical electronic layouts are based on simple rectangular features. The resulting geometries can be simulated using electromagnetic solvers, which can be quite computationally heavy.

Today, photonic design is gradually migrating to the circuit level [152]: instead of defining and simulating every individual geometry, a photonic circuit is constructed of building blocks and connected with waveguides. Each building block has an efficient compact model which is used to calculate the reponse of the entire circuit. This is similar to electronic circuit design, where compact models are defined in SPICE or VerilogA. Photonic models can also be defined in VerilogA [196], or in a model for a specialized photonic circuit simulator. Such circuit-level design, which starts with a schematic and circuit simulation, and only then implements the circuit as an actual layout, can scale up to designs of much larger complexity. Also, circuit-level design allows the user to focus on the added value of his application, rather than redesigning low-level functional building blocks.

Circuit design requires a library of components that can be connected together into a circuit. For each technology platform, fabs supply a PDK which contains a standard component library for essential functions such as waveguiding, splitting, crossing, modulation, detection and fiber coupling. Until recently, these component libraries consisted of simple layouts that a designer could reuse at the circuit level, but the PDK libraries are now gradually populated with compact models for the building blocks, enabling designers to verify the circuit function in simulation.

Most photonic design tools are available as commercial software. Unfortunately, at this point there is only limited interoperability between tools of different vendors, even though some collaboration and standardization activities are emerging [197]. This also extends to integration of photonic design tools and *electronics design automation* (EDA) tools, as we see EDA vendors gradually supporting photonic design [198], [199].

Because high-contrast silicon photonics components are so geometry sensitive, it is important that the effects of the fabrication process are taken into account at the design stage. *Design for manufacturability* (DfM) techniques that originated

in electronics are now being adapted and extended for photonics. This includes *litho-friendly design* (LFD) [200], tolerant circuit design [63], use of optical proximity corrections [201] and tiling to control pattern densities [202].

To obtain a *first-time-right* design, an effective verification strategy is needed. This consists of two steps: *Design rule checking* (DRC) ensures that the layed-out design can actually be fabricated, while *layout-vs-schematic* (LVS) tests extract the functional circuit from a layout and compare it to the original design intent, including simulation of the extracted circuit. Robust layout verification flows have also been under development to ensure that both the mask fabrication and silicon processing will not be affected by the inclusion of designs which are not qualified [61].

The landscape of design tools and PDKs is rapidly evolving, with new capabilities for designers being released every few months. This is needed, because a low-threshold design experience is a direct enabler to open-access technology.

- 3) Packaging: The packaging of silicon photonics chips is of critical importance both at the prototyping and the manufacturing level. Efforts have been made in standardizing the packaging processes to reduce the cost of packaging and to improve the reliability issues associated with optical and electrical interfaces to silicon photonics chips. Passive and automated packaging schemes are developed to cut the cost associated with photonics packaging [203]. Similar to PIC layout design rules, there have been efforts to develop packaging design kits and packaging design rules for costeffective packaging of silicon photonics chips, their thermal management, integration with electronics and assembly of off-chip light sources. Recently, the open-access Photonic Integrated Circuit Assembly and Packaging Pilot line (PIXAPP) has been established in Europe to provide end-users easy access to the packaging of PICs. Similar initiatives are emerging in other continents. For example, the open-access platform of AIM Photonics [149] and the one from Sandia National Laboratories are combined with chip scale assembly and packaging service.

- 4) Emerging Silicon PIC Prototyping & Manufacturing Initiatives: The success and impact ePIXfab created by pioneering open-access silicon photonics technologies acted as a blueprint for various other players. With a growing number of initiatives, such as OpSIS and A\*STAR IME, imitated this success and resulted in creating a much broader and active community engaged in PIC-based R&Development. Though OpSIS has ceased and ePIXfab handed over its brokering role to Europractice and CMP, the ePIXfab members (IMEC, CEA-LETI, IHP, VTT) and A\*STAR IME continue to consolidate their respective technologies by the inclusion of new process modules and enhancing their TRLs.

Recent years have seen numerous new initiatives by CMOS pilot lines and public/private research institutes to provide open-access silicon photonics technologies. For example,in Europe, the pilot lines *PIX4Life* providing PIC prototyping/manufacturing for life-science applications and *MIRPHAB* for mid-IR applications have surfaced. *A\*STAR IME*, which is pioneering Asian institute providing open-access silicon photonics, has started a spin-off *Advanced Micro Foundry* (AMF) in 2017 to provide manufacturing of silicon PICs

using the processes and technology developed by A\*STAR IME. In Japan the PETRA initiative, in Korea Electronics and Telecommunications Research Institute (ETRI) and in China IMECAS have started providing silicon PIC platforms to their domestic end-users. In North America, Sandia Research Laboratories and AIM Photonics have made progress to develop and offer silicon photonics platforms. Anticipation a demand for high-volume PIC-manufacturing, CMOS pilot lines and research institutes have developed routes for high-volume manufacturing through commercial fabs. Moreover, commercial fabs have developed silicon photonics PIC platforms and started offering them to third-party end-users.

## V. SUMMARY

Open-access of silicon photonics technologies, initially offered by CMOS research institutes, has played an instrumental role in making it a mainstream photonic integration technology. Thanks to the continuous consolidation of the technology platforms offered by CMOS pilot lines and research institutes, low-volume manufacturing of silicon photonics PICs is already happening. The number of fabless companies envisaging silicon photonics products and requiring the manufacturing of their products is rapidly increasing. With this clear trend in market growth and looming demand for high-volume manufacturing by fabless companies, pure-play foundries have started offering open-access silicon photonics technologies for prototyping as well as manufacturing at low- and high-volume level.

The potential penetration of silicon photonics into market sectors beyond optical communication further augments the growth of silicon photonics. The flavour of silicon photonics geared towards visible wavelengths and mid-infrared wavelengths respectively have emerged to address life-science and sensing applications. There are cases where the different flavors of silicon photonics compete with each other, making the technology more agile for evolution and there are cases where these flavors complement each other to strengthen silicon photonics against competing technologies. Since silicon photonics is also viable at moderate volumes, many of the existing silicon photonics flavors may grow industrially even if they target specialized applications.

The developments made by the open-access technology platforms have galvanized the silicon photonics eco-system. A mature and complete supply chain from design to packaging and testing is imminent.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. Timo Aalto (VTT), Prof. John Bowers (University of California, Santa Barbara), Dr. Chris Doerr (Acacia Communications, Inc.), Dr. Jean-Marc Fedeli (CEA-LETI), Dr. Patrick Lo Guo-Qiang (Advanced Micro Foundry), Dr. Amit Khanna (Elenion Technologies), Prof. Thomas Koch (The University of Arizona), Prof. Joyce Poon (University of Toronto), Prof. Hon Ki Tsang (The Chinese University of Hong Kong) and Prof. Lars Zimmermann (IHP) for their kind inputs to improve the quality of this manuscript.

#### REFERENCES

- M. Salib et al., Silicon Photonics, Intel Technology Journal, Vol. 8, Issue 2, p143-160, May 2004.

- [2] W. Bogaerts et al., Nanophotonic waveguides in silicon-on-insulator fabricated with CMOS technology, Journal of Lightwave Technology, vol. 23, no. 1, pp. 401-412, Jan. 2005.

- [3] B. Jalali and S. Fathpour, Silicon Photonics, Journal of Lightwave Technology, vol. 24, no. 12, pp. 4600-4615, Dec. 2006.

- [4] A. Rickman, The commercialization of silicon photonics, Nature Photonics, Volume 8, 2014.

- [5] A. Huang et al., A 10Gb/s photonic modulator and WDM MUX/DEMUX integrated with electronics in 0.13/spl μm SOI CMOS, 2006 IEEE International Solid State Circuits Conference - Digest of Technical Papers, San Francisco, CA, 2006, pp. 922-929.

- [6] K. Greene, Silicon Photonics Comes to Market, MIT Technology Review, https://www.technologyreview.com/s/408520/ silicon-photonics-comes-to-market/, Aug. 2007.

- [7] M. Paniccia et al., Integration challenge of silicon photonics with microelectronics, IEEE International Conference on Group IV Photonics, 2005. 2nd, Antwerp, Belgium, 2005, pp. 20-22.

- [8] A. Liu et al., A high-speed silicon optical modulator based on a metaloxidesemiconductor capacitor, Nature volume 427, pages 615618 (12 February 2004).

- [9] D. J. Thomson et al., Roadmap on silicon photonics, J. Opt. 18 073003, 2016.

- [10] Yole, Silicon Photonics 2018

- [11] M. A. G. Porcel et al., Monolithic photonic integration for visible and short near-infrared wavelengths: technologies and platforms for bio and life science applications, Advanced Optical Technologies, Vol. 7, no. 1-2, 2018

- [12] A. Jovic et al., A MEMS Actuator System for an Integrated 3-D Optical Coherent Tomography Scanner, Journal of Microelectromechanical Systems, vol. 27, no. 2, pp. 259-268, April 2018.

- [13] Y. Li et al., Six-beam homodyne laser Doppler vibrometry based on silicon photonics, Opt. Express 26, 3638-3645 (2018).

- [14] C. V. Poulton et al., Coherent solid-state LIDAR with silicon photonic optical phased arrays, Opt. Lett. 42, 4091-4094 (2017).

- [15] A. Martin et al., Photonic Integrated Circuit-Based FMCW Coherent LiDAR, Journal of Lightwave Technology, vol. 36, no. 19, pp. 4640-4645, Oct.1, 2018.

- [16] A. N. Tait et al., Neuromorphic photonic networks using silicon photonic weight banks, Scientific Reportsvolume 7, Article number: 7430 (2017).

- [17] M. Lukosevicius et al., Reservoir Computing Approaches to Recurrent Neural Network Training, Computer Science Review, vol. 3, no. 3, pp. 127, 2009.

- [18] C.-S. Poon et al., Neuromorphic silicon neurons and large-scale neural networks: challenges and opportunities. Front. Neurosci. 5, 108 (2011).

- [19] N. C. Harris et al., Programmable Nanophotonics for Quantum Simulation and Machine Learning, Advanced Photonics 2017 (IPR, NOMA, Sensors, Networks, SPPCom, PS), OSA Technical Digest (online) (Optical Society of America, 2017), paper ITu3A.3.

- [20] Y. Shen et al., Deep learning with coherent nanophotonic circuits, Nature Photonics volume 11, pages 441446 (2017).

- [21] A. Peruzz et al., Quantum Walks of Correlated Photons, Science, 17 Sep 2010: Vol. 329, Issue 5998, pp. 1500-1503.

- [22] S. Paesani et al., Experimental quantum hamiltonian learning using a silicon photonic chip and a nitrogen-vacancy electron spin in diamond, 2017 Conference on Lasers and Electro-Optics Europe & European Quantum Electronics Conference (CLEO/Europe-EQEC), Munich, 2017, pp. 1-1.

- [23] https://www.mosis.com/

- [24] P. Absil et al., Reliable 50Gb/s Silicon Photonics Platform for Next-Generation Data Center Optical Interconnects, 63<sup>rd</sup> International Electronic Device Meeting, San Francisco, CA, 2017.

- [25] A. E. J. Lim et al., Path to silicon photonics commercialization: 25 Gb/s platform development in a CMOS manufacturing foundry line, OFC 2014, San Francisco, CA, 2014, pp. 1-3.

- [26] B. Szelag et al., Multiple wavelength silicon photonic 200 mm R+D platform for 25Gb/s and above applications, Proceedings Volume 9891, Silicon Photonics and Photonic Integrated Circuits V; 98911C (2016); doi: 10.1117/12.2228744, Event: SPIE Photonics Europe, 2016, Brussels, Belgium

- [27] D. Knoll et al., BiCMOS silicon photonics platform for fabrication of high-bandwidth electronic-photonic integrated circuits, 2016 IEEE 16th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Austin, TX, 2016, pp. 46-49.

- [28] E. Timurdogan et al., AIM Process Design Kit (AIMPDKv2.0): Silicon Photonics Passive and Active Component Libraries on a 300mm Wafer, Optical Fiber Communication Conference, OSA Technical Digest (online) (Optical Society of America, 2018), paper M3F.1.

- [29] T. Aalto et al., 3 Micron Silicon Photonics, OFC 2018, San Francisco, CA, 2018, pp. 1-3.

- [30] V. Stojanovi et al., Monolithic silicon-photonic platforms in state-ofthe-art CMOS SOI processes [Invited], Opt. Express 26, 13106-13121 (2018).

- [31] T. Horikawa et al., A 300-mm Silicon Photonics Platform for Large-Scale Device Integration, IEEE Journal of Selected Topics in Quantum Electronics, vol. 24, no. 4, pp. 1-15, July-Aug. 2018, Art no. 8200415.

- [32] T. Liow et al., Silicon Modulators and Germanium Photodetectors on SOI: Monolithic Integration, Compatibility, and Performance Optimization, IEEE Journal of Selected Topics in Quantum Electronics, vol. 16, no. 1, pp. 307-315, Jan.-feb. 2010.

- [33] P. Dumon, Towards Fabless Silicon Photonics, Frontiers in Optics 2008/Laser Science XXIV/Plasmonics and Metamaterials/Optical Fabrication and Testing, OSA Technical Digest (CD) (Optical Society of America, 2008), paper FMG1.

- [34] M. Hochberg et al., Silicon Photonics: The Next Fabless Semiconductor Industry, in IEEE Solid-State Circuits Magazine, vol. 5, no. 1, pp. 48-58, winter 2013.

- [35] J. Pond et al., A simulation tool development roadmap to support a scalable silicon photonics design ecosystem, 2015 IEEE 12th International Conference on Group IV Photonics (GFP), Vancouver, BC, 2015, pp. 189-190.

- [36] M. Smit et al., An introduction to InP-based generic integration technology, Semiconductor Science and Technology, vol. 29, no. 8, Jun. 13, 2014.

- [37] Andy Eu-Jin Lim et al., Path to Silicon Photonics Commercialization: The Foundry Model Discussion, Silicon Photonics III Systems and Applications Editors: Pavesi, Lorenzo, Lockwood, David J (Eds.), 2016.