# Transfer Printing of Silicon-on-Insulator Devices on Silicon Nitride Waveguide Circuits: Design of Coupling Structures and Process Development

Grigorij Muliuk<sup>1,2,\*</sup>, Nan Ye<sup>1,2</sup>, Sarah Uvin<sup>1,2</sup>, Antonio Trindade<sup>3</sup>, Chris Bower<sup>4</sup>, Dries Van Thourhout<sup>1,2</sup>, Günther Roelkens<sup>1,2</sup>

<sup>2</sup> Center for Nano- and Biophotonics (NB-Photonics), Ghent University, Belgium <sup>3</sup> X-Celeprint Limited, Cork, Ireland <sup>4</sup> X-Celeprint Inc., Research Triangle Park, NC, USA

The use of transfer printing technology to integrate active silicon photonic components on a silicon nitride waveguide circuit is proposed. Alignment tolerant coupling schemes were designed using full vectorial simulations. Adiabatic taper structures allow 80% coupling efficiency at 1  $\mu$ m misalignment for the O-band and 97% for the C-band. Compact directional coupler structures allow 80% efficiency for 1  $\mu$ m misalignment for both bands. We present first transfer-printing technology results. This includes the release, picking and printing of silicon coupons from an SOI source wafer to a silicon target wafer. The impact of stress in the silicon membrane on the transfer printing process is assessed.

### Introduction

Silicon-based photonic integrated circuits (PICs) are especially attractive for realizing optical transceivers because of the use of CMOS fabrication technology, resulting in high-yield, low-cost, high-speed photonic devices [1] that can be fabricated in a large volume. However, silicon has some drawbacks including the high thermo-optic coefficient of silicon, the relatively large waveguide propagation losses [2] and the lack of an industrially available scalable integration of III-V devices. Silicon nitride (SiN) waveguide circuits are rapidly evolving. Their main advantages are the lower propagation loss due to the lower refractive index contrast and about 5x lower thermo-optic coefficient [3]. Therefore, the ideal solution would be the co-integration of SiN waveguide circuits and Si photonic devices. While a SiN waveguide layer can be incorporated in the silicon photonics process flow, the larger footprint of these devices makes this a not very economical solution.

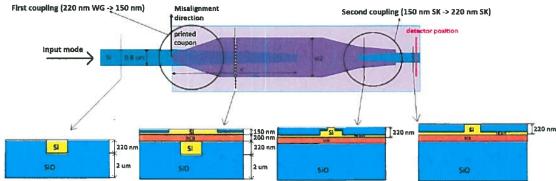

Fig. 1. Simulated Si-to-Si adiabatic taper coupling scheme.

<sup>&</sup>lt;sup>1</sup> Photonics Research Group, INTEC Department, Ghent University-IMEC, Technologiepark 15, 9052 Zwijnaarde, Belgium

<sup>\*</sup> Corresponding author: grigorij muliuk@intec.ugent.be;

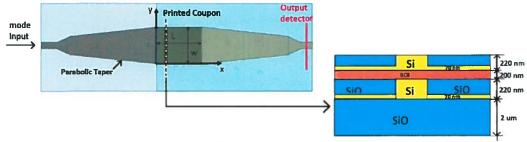

Fig. 2. Simulated Si-to-Si directional coupler coupling scheme.

Micro-transfer-printing (µTP or transfer printing), proposed by Rogers et al. [4] is a novel technology in which materials or devices can be selectively removed from their source wafer and transferred in a massively parallel way to a new substrate. This technique can therefore be used to transfer print silicon photonic devices, fabricated in dense arrays on a silicon photonic source wafer, to a SiN target wafer. Transfer printing still requires additional process development for integrating Si optical devices on SiN PICs. This includes the development of releasing, picking and printing of the silicon photonic components. An important issue is the print misalignment, which is 3σ value. This requires the development of alignment tolerant, compact and broadband (covering C-band and O-band) optical interfaces. This paper focuses on simulations of these structures and first results of the Si transfer printing process development.

## Coupling between SiN to Si.

Efficient coupling between SiN and Si waveguides has already been demonstrated for the 1310 nm and 1550 nm wavelength range using adiabatic taper structures. However, the existing designs are not transfer printing compatible as insufficient alignment tolerance is provided by these structures. Therefore, the following coupling scheme is proposed: the mode, propagating in the SiN waveguide couples to a Si layer via adiabatic coupling transition. This silicon waveguide structure is lithographically aligned to the SiN waveguide structure. Then this mode couples to the SOI device transfer printed to the target wafer using a divinylsiloxane-bis-benzocyclobutene (BCB) bonding agent. Therefore, the optical interface of interest is one between two silicon waveguide layers.

# Alignment tolerant coupling structures

As both mode guiding layers are silicon, the refractive indices are the same and hence a phase-matching condition can be simply implemented. Therefore, an adiabatic taper approach can be considered. The coupling structure is depicted in Fig. 1. The first transition consists of a 220 nm fully-etched (WG) input waveguide on the target wafer coupled into a 150 nm thick shallow etched (SK) waveguide on the printed device side. The second transition happens in the printed coupon: 150 nm SK to 220 nm SK coupling. Here a coupling efficiency of 99 % can be easily obtained. The silicon taper on the target wafer tapers from 800 nm width to 150 nm width, while the taper on the silicon coupon tapers from 150 nm to a width w2 over a length of 200 um.

When both guiding layers are silicon and the propagation constants are matched, a directional coupler structure can be implemented: two identical waveguides placed in close proximity can lead to a complete optical power exchange. We can implement this here using two symmetric 220 nm SK waveguides, the schematics of which are depicted in Fig. 2.

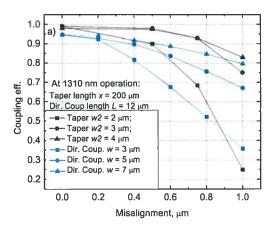

Fig. 3. a) Misalignment simulations, sweeping over taper or directional coupler widths; b) Bandwidth simulations of adiabatic taper and directional coupler structures.

The coupling efficiency of the adiabatic taper structure simulated by FDTD taking into account a misalignment of the printed coupon along the y-axis is shown in Fig. 3 a), together with the simulation results of the directional coupler structure, simulated using FIMMPROP. A 1310 nm TE polarized input mode is assumed in these simulations.

The waveguide dimensions have a big impact on the results. Especially the waveguide width is very important for achieving good alignment tolerance: for an adiabatic taper length of 200  $\mu m$  and a taper width of 4  $\mu m$ , one can achieve >80% coupling efficiency at  $\pm 1~\mu m$  misalignment. In the case of a directional coupler structure, power exchange happens in a very short region (12  $\mu m$  length for 1310 nm). Using a 7  $\mu m$  wide waveguide, one can achieve 80% coupling efficiency at  $\mu m$  misalignment. In order to efficiently couple the light into this wide waveguide, one can employ parabolic taper structures both on the source and target layer (see Fig. 2).

Bandwidth simulations (Fig. 3 b)) show that adiabatic tapers are optically broadband, covering both the C-band and O-band, providing at 1550 nm even 97 % efficiency at  $\pm 1~\mu m$  misalignment. For the case of directional couplers two separate coupling lengths have to be used for different bands:  $L=12~\mu m$  for O-band and  $L=20~\mu m$  for C-band.

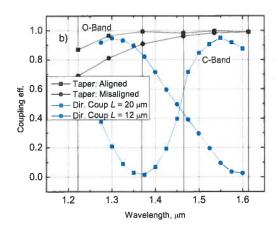

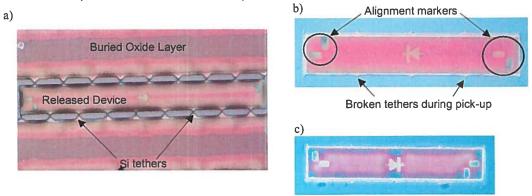

Fig. 4. a) Microscope image of a released coupon on SOI substrate; b) Printed coupon before curing; c) Printed coupon after curing.

### Transfer printing results

Transfer printing tests were performed on standard silicon-on-insulator (SOI) substrates.  $SiO_2$  was deposited using plasma enhanced chemical vapor deposition (PECVD) method and patterned using buffered hydrofluoric acid (BHF). This way we emulate a silicon photonic device with a back-end stack. 1  $\mu$ m PECVD amorphous silicon (a-Si) was then deposited which acted as a protection layer. Tether structures were formed in the amorphous silicon to support the device when releasing it from the silicon source wafer. Using dry etching the buried oxide was exposed. Then samples were dipped for ~65 min in BHF to remove the buried oxide layer, thereby making the silicon device layer free standing, still supported by silicon tethers. At last, the a-Si protection layer was removed using plasma etching.

A picture of the test device can be seen in Fig. 4 a). This device ( $500x60 \mu m$  in size) consists of 220 nm silicon and a top SiO<sub>2</sub> layer and is suspended on triangular tether structures, which are anchored to the barrier silicon region not fully under-etched.

Using a PDMS stamp, these devices can be picked from the source wafer (by breaking the tethers) and transferred to a target wafer. Devices were printed on silicon substrates with 100 nm PECVD SiO<sub>2</sub> and a 50 nm layer of BCB. Fig. 4 b) shows a microscope image of the printed device. One can clearly see that during pick-up the tethers break at the narrowest point. The device adheres well to the target wafer. After curing the BCB in an oven, one can see a non-uniformity in the color on the sides of the device (Fig. 4 c)). This might be related to the BCB non-uniformity that appear during printing of a bended device. Bending might be related to compressive stress of the PECVD silicon oxide on top of the coupon and hence stress-compensation layers will be added in a later stage to cope with this effect.

### **Conclusions**

Simulation results of two novel alignment tolerant silicon-to-silicon coupling schemes were presented. The first coupler makes use of an adiabatic taper transition - light couples from a narrow, 220 nm fully etched waveguide to a 150 nm thick waveguide on the shallow-etched transfer-printed film. 200 µm long and 4 µm wide tapered waveguides can provide efficient coupling at 1 µm printing misalignment both for O- band and C- band. The second coupler relies on a directional coupler structure, which makes use of two symmetric shallow-etched waveguides. Good alignment tolerance is obtained for wide waveguides. Separate coupler lengths for 1310 nm and 1550 nm bands have to be used. First transfer printing tests were carried out. Successful tether design, complemented with under-etching, picking and printing processes were obtained. A high printing yield requires reduction of the stress in the silicon coupons by implementing stress compensation layers.

### References

- [1] N. Izhaky, M. T. Morse, Member, S. Koehl, O. Cohen, D. Rubin, A. Barkai, G. Sarid, R. Cohen, M. J. Paniccia. "Development of CMOS-Compatible Integrated Silicon Photonics Devices". ," J. Sel. Top. Quantum Electron., VOL. 12, NO. 6, 2006.

- [2] W. Bogaerts, P. Dumon, D. Van Thourhout, D. Taillaert, P. Jaenen, J. Wouters, S. Beckx, V. Wiaux, and R. Baets, "Compact wavelength selective functions in silicon-on-insulator photonic wires," J. Sel. Top. Quantum Electron., vol. 12, no. 6, pp. 1394–1401, December 2006.

- [3] S. Romero-García, F. Merget, F. Zhong, H. Finkelstein, J. Witzens. "Silicon nitride CMOS-compatible platform for integrated photonics applications at visible wavelengths". Optics Express. 14036, 2013.

- [4] X. Feng, M. A. Meitl,‡ A. M. Bowen, Y. Huang, R. G. Nuzzo, J. A. Rogers, "Competing Fracture in Kinetically Controlled Transfer Printing". Langmuir, 23, 12555-12560, 2007.